3D TSVデバイス市場 規模・シェア分析 – 成長トレンドと予測 (2025年~2030年)

3D TSVデバイス市場レポートは、製品タイプ(イメージングおよび光電子、メモリなど)、TSV技術(ビアミドル、ビアラスト、ビアファースト)、ウェーハサイズ(200mm以下、300mm、450mm)、エンドユーザー産業(家庭用電化製品、自動車、IT・通信など)、および地域(北米、南米、欧州など)別に分類されます。市場予測は金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

3D TSVデバイス市場概要

3D TSV(Through-Silicon-Via)デバイス市場は、高性能コンピューティング、AIアクセラレーター、先進運転支援システム(ADAS)からの持続的な需要に支えられ、急速な成長を遂げています。米国、欧州、韓国における政府補助金が製造施設の拡張を加速させており、ロジックとメモリのコパッケージング、ハイブリッドボンディング、チップレット対応インターポーザー設計といった技術革新が帯域幅のボトルネックを解消し、TSVピッチを20ミクロン以下に縮小しています。深掘り反応性イオンエッチングや銅充填のためのツール需要は高く、アウトソーシング組立・テスト(OSAT)企業と統合デバイスメーカー(IDM)の間で、ハイパースケーラーやティア1自動車サプライヤーとの長期契約を巡る競争が激化しています。シリコンフォトニクス・コパッケージングや埋め込み型医療センサーといった、小規模ながら急速に成長している分野も、市場に新たな価値創造の機会を提供しています。

市場規模と成長予測

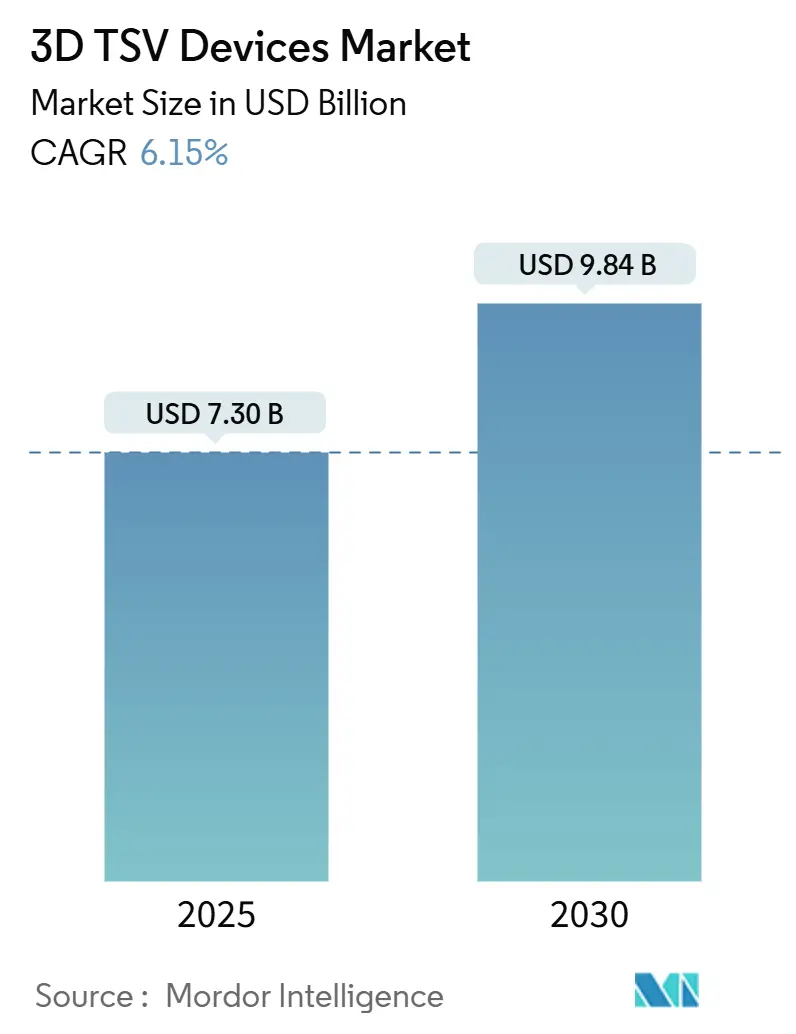

2025年には73億米ドルに達すると予測される3D TSVデバイス市場は、2030年までに98.4億米ドルに成長し、予測期間中の年平均成長率(CAGR)は6.15%と見込まれています。アジア太平洋地域が最も急速に成長し、最大の市場であり続けると予測されています。市場の集中度は中程度です。

主要なレポートのポイント

* 製品タイプ別: 2024年にはメモリが市場の46.3%を占め、3D TSVデバイス市場を牽引しました。MEMSおよびセンサーは2030年までに8.71%のCAGRで成長すると予想されています。

* TSV技術別: 2024年にはビアミドルが収益の54.8%を占めましたが、ビアファーストは2030年までに7.83%のCAGRで拡大すると予測されています。

* ウェハーサイズ別: 2024年には300mm基板が市場の58.8%を占めました。450mmセグメントは8.01%のCAGRで成長しています。

* エンドユーザー産業別: 2024年にはITおよび通信が市場の38.02%を占めましたが、自動車セグメントが9.31%のCAGRで最も急速に成長しています。

* 地域別: 2024年にはアジア太平洋地域が世界の収益の43.12%を占め、2030年までに8.73%のCAGRで成長すると予測されています。北米がこれに続き、CHIPS法による61.65億米ドルの資金援助がTSVパッケージングの国内生産を促進すると期待されています。

市場トレンドと洞察(促進要因)

* 高性能コンピューティングとAIワークロードの需要増加: 大規模言語モデルのトレーニングが1兆パラメータを超え、メモリ階層はGDDR6を超えた進化を余儀なくされています。SK Hynixの12層HBM4スタックは2.1 Tbit/sの帯域幅を実現し、JEDECのHBM4標準は2048ビットインターフェースを規定しており、これはTSVアーキテクチャのみが対応可能です。MicronはHBM収益が倍増し、Samsungは銅-銅ハイブリッドボンディングでビア抵抗を40%削減しています。IntelのGaudi 3アクセラレーターはHBM3Eスタックを統合し、CHIPS法による大規模なパッケージング投資を促しています。

* データセンターの拡張による高帯域幅メモリ(HBM)の採用: ハイパースケーラーはAIサーバーを記録的な速度で展開しており、NVIDIA H200やAMD MI300Xソケットはそれぞれ80GB以上のHBM3を消費します。TSMCのCoWoSラインは2024年を通じて100%以上の稼働率を維持し、大規模な拡張投資が行われています。MicronのHBM供給は2025年まで完全に予約済みであり、平均販売価格を30%押し上げる可能性があります。

* スマートフォンと家電製品の急速な小型化: プレミアムスマートフォンは8mm以下の薄さを目指しており、Sonyの積層CMOSイメージセンサーはビアラストTSVを利用して画素面積を犠牲にすることなくロジックを接続し、低照度感度を向上させています。AppleのA18 ProはInFO-PoPとビアファーストTSVを使用してZ軸の高さを削減し、QualcommのSnapdragon 8 Gen 4はマイクロTSVを介してLPDDR5Tと組み合わせ、オンデバイスAI向けに9.6 GT/sのデータレートを維持しています。

* チップレットベースのヘテロジニアス統合アーキテクチャ: ロジックノードがスケーリング限界に近づくにつれて、チップレットによる分離が各タイルに最適なプロセス利用を可能にしています。AMDのZen 5 CPUは3D V-CacheをビアミドルTSVで積層し、レイテンシを削減しゲームのフレームレートを向上させています。IntelのMeteor LakeはFoverosベースダイを使用し、UCIe 1.1仕様はTSV相互接続に依存するダイ間リンクを標準化しています。

* シリコンフォトニクスにおける3Dインターポーザー積層の必要性: シリコンフォトニクスは、1.6 Tb/sイーサネットなどの高速データ転送のためにTSVインターポーザーを必要としており、この分野での需要が高まっています。

* 先進パッケージングファブへの政府補助金: 米国のCHIPS Act、欧州、韓国などの政府補助金が、先進パッケージングファブの建設と拡張を強力に後押ししています。

市場の制約

* 3D TSVパッケージの高コスト: TSVアセンブリはデバイスあたり15~40米ドルの追加コストを発生させ、ミッドレンジのスマートフォンやIoTデバイスの利益率を圧迫しています。エッチングツールや電解めっきシステムは高価であり、認定サイクルも長く、市場投入までの期間を最大16週間延長する可能性があります。

* 熱による信頼性と歩留まりの課題: HBM4スタックは5×7mmのフットプリントで15W以上を放熱し、85℃で80µmの反りを引き起こすことがあります。ハイブリッドボンディングの歩留まりは銅の平坦度仕様に制約され、IntelのFoveros Directではボイド形成が主要な欠陥となっています。TSVベースのDRAMはテスト時間が長く、追加コストが発生します。

* TSVエッチングおよび充填ツールのサプライチェーンボトルネック: TSV製造に必要な特殊ツールのサプライチェーンにボトルネックが生じることがあり、特にアジア太平洋地域と北米で顕著です。

* TSV化学物質に対する環境規制の強化: フッ素系化学物質に対する環境規制が厳しくなっており、特に欧州と北米で、TSV製造プロセスに影響を与えています。

セグメント分析

* 製品タイプ別: メモリデバイスは、AIアクセラレーター向けHBMのデファクトスタンダード化により、市場の主要な収益源となっています。MEMSおよびセンサーは、自動車レーダーや慣性ユニットの採用により成長が見込まれます。イメージングおよび光電子工学は、ソニーの裏面照射型センサーに代表されるビアラストTSVの恩恵を受けています。マイクロLEDディスプレイ向けにビアファーストTSVが利用されていますが、歩留まりが課題です。

* TSV技術別: ビアミドルはDRAMやCISの成熟度により主流ですが、チップレットベースのダイがサブ1µmのオーバーレイ精度を要求するため、ビアファーストが成長しています。ビアラストはセンサーにとって重要であり、ハイブリッドボンディングは2026年以降に相互接続密度を倍増させ、TSVの役割を確固たるものにするでしょう。

* ウェハーサイズ別: 300mmウェハーは世界中で120以上の認定ファブに支えられ、量産を牽引しています。450mmセグメントはまだ小さいものの、TSMCとSamsungがパイロットラインを検証しており、成長が見込まれます。Intelは450mmの予算を先進パッケージングに振り向け、TSVとチップレットの組み合わせがより良い投資収益率をもたらすという業界のコンセンサスを裏付けています。

* エンドユーザー産業別: ITおよび通信が最大のシェアを維持していますが、自動車セグメントが最も急速に成長しており、ADAS、インフォテインメント、バッテリー管理を統合するEVドメインコントローラーが牽引しています。家電製品は積層CISやLPDDRの需要を維持し、ヘルスケア分野ではTSV対応の埋め込み型デバイスが開発されています。航空宇宙および防衛分野では、放射線耐性のあるTSVメモリが利用されています。

地域分析

* アジア太平洋: 2024年には収益の43.12%を占め、8.73%のCAGRで拡大しています。TSMCのCoWoS容量の70%以上、SamsungのHBMの45%のシェア、SK Hynixの垂直統合が成長を牽引しています。日本の補助金、中国のYMTCの3D NANDコントローラー積層への関心、韓国の税制優遇、インドのMicronによるOSAT施設投資などが、アジアを3D TSVデバイス市場の中心地として確立しています。

* 北米: 2024年には約28%を占めました。MicronはCHIPS Actの下でHBMファブ建設のために61.65億米ドルを獲得し、Amkorはアリゾナ州に300mm TSVパッケージング工場を建設中です。IntelはFoveros容量を拡張し、カナダはコパッケージドオプティクスパイロットラインに投資しています。

* 欧州: 2024年には約18%を占めました。STMicroelectronicsはフランスで300mm TSVラインを拡張するために29億ユーロを確保し、InfineonはドレスデンでGaNパワーデバイス向けにビアミドルTSVを認定しました。Fraunhofer IZMはハイブリッドボンディングによる0µmピッチを達成し、英国はEVインバーター向けGaN TSVラインに投資しています。

* 南米およびMEA: 両地域合わせて5%未満ですが、ブラジルとUAEは2027年以降の容量追加を示唆しています。

競合状況

市場集中度は中程度から高く、上位5社が市場価値の約75%を占めています。TSMCは高性能コンピューティング向け先進パッケージングの70%以上を占め、NVIDIA、AMD、Broadcomなどの主要顧客を獲得しています。SamsungとSK HynixはHBM市場の85%を供給し、垂直積層技術を活用して顧客を長期契約にロックインしています。MicronはCHIPS Actによる資金援助を受けて、2027年までに生産能力を拡大し、差を縮めています。

OSAT大手であるASE、Amkor、JCETは、ファブレスチップレット設計者を引き付けるために300mmファンアウトおよびTSVラインを拡張しています。シリコンフォトニクス・コパッケージングなどのニッチな分野では、CiscoやIntelが1.6 Tb/sイーサネット向けにTSVインターポーザーを必要としており、新たな機会が生まれています。高い設備投資とTSV化学物質に関する特許が参入障壁となり、既存企業の価格決定力を維持しています。

主要プレイヤー

* Taiwan Semiconductor Manufacturing Company Limited

* Samsung Electronics Co., Ltd.

* Intel Corporation

* Micron Technology, Inc.

* SK hynix Inc.

最近の業界動向

* 2025年4月: SK Hynixが2 Tbit/sを超える帯域幅を持つ12層HBM4サンプルを発表し、2026年後半に量産開始を予定しています。

* 2025年3月: AmkorがCHIPS法から4.07億米ドルの資金援助を受け、20億米ドル規模のアリゾナTSV工場建設を開始しました。2027年の稼働開始を予定しています。

* 2025年2月: Samsungが平沢のハイブリッドボンディングHBM4ラインに3兆韓国ウォンを投じ、2025年後半にパイロット生産を開始する予定です。

* 2025年1月: Intelがニューメキシコ州とアリゾナ州への35億米ドルの投資を通じて、2026年までにFoveros Directの生産能力を3倍にすると発表しました。

* 2024年12月: TSMCが28億米ドルのCoWoS拡張を発表し、2025年後半までに月産6万枚のウェハー処理能力を目指しています。

このレポートは、グローバル3D TSV(Through-Silicon Via)デバイス市場に関する詳細な分析を提供しています。市場の定義、調査範囲、調査方法から、市場の現状、将来予測、競争環境、機会までを網羅しています。

市場の成長を牽引する主要な要因としては、高性能コンピューティングおよびAIワークロードに対する需要の増加、データセンターの拡大による高帯域幅メモリ(HBM)の採用促進、スマートフォンや家電製品における急速な小型化が挙げられます。また、チップレットベースのヘテロジニアス統合アーキテクチャの進展、シリコンフォトニクスにおける3Dインターポーザスタッキングの必要性、そして先進パッケージング工場に対する政府補助金も重要な推進力となっています。

一方で、市場の成長を抑制する要因も存在します。3D TSVパッケージの高いユニットコスト、熱に起因する信頼性および歩留まりの課題、TSVエッチングおよび充填ツールのサプライチェーンにおけるボトルネック、そしてTSV化学物質に対するより厳格な環境規制がこれに該当します。

市場は、製品タイプ、TSV技術、ウェーハサイズ、エンドユーザー産業、および地域別に詳細にセグメント化され、その価値(USD)に基づいて予測されています。製品タイプ別では、イメージングおよび光電子デバイス、メモリ、MEMS/センサー、LED、その他の製品が含まれます。TSV技術別では、Via-Middle TSV、Via-Last TSV、Via-First TSVが分析対象です。ウェーハサイズ別では、200mm以下、300mm、450mmの各サイズが考慮されています。エンドユーザー産業別では、家電、自動車、ITおよび通信、ヘルスケア、航空宇宙および防衛、その他の産業が対象です。地域別では、北米、南米、欧州、アジア太平洋、中東およびアフリカが詳細に分析されています。

レポートの主要な調査結果と予測は以下の通りです。

* 高帯域幅メモリ(HBM)の需要は2024年に倍増し、これが2030年までの3D TSV市場全体の年平均成長率(CAGR)6.15%を牽引しています。

* チップレット設計において最も注目されているTSV技術はVia-First TSVであり、ベースダイがサブ1 µmのオーバーレイ精度を要求するため、7.83%のCAGRで拡大すると予測されています。

* 自動車産業は、電気自動車のドメインコントローラーが積層型センサーフュージョンプロセッサを必要とすることから、最も急速に成長する垂直市場と見なされており、TSV需要は9.31%のCAGRで増加する見込みです。

* 政府のインセンティブは、設備投資の拡大に重要な役割を果たしています。米国のCHIPS法や欧州・アジアの同様のプログラムは、数十億ドル規模のTSV工場建設を支援し、オンショア供給を加速させています。

* 先進パッケージングにおけるサプライヤーの集中度は高く、上位5社が収益の約75%を占めており、市場集中度スコアは10点中7点と評価されています。

* 450mmウェーハのTSV生産は現在パイロットラインが存在するものの、ツールエコシステムが成熟する2028年以前に本格的な採用が始まる可能性は低いとされています。

競争環境の分析では、市場の集中度、主要企業の戦略的動向、市場シェアが評価されています。台湾積体電路製造(TSMC)、Samsung Electronics、Intel Corporation、Micron Technology、SK hynixなど、多数の主要企業がプロファイルされており、グローバルおよび市場レベルの概要、主要セグメント、財務情報、市場ランク/シェア、製品とサービス、最近の動向が提供されています。

本レポートは、市場の機会と将来の展望についても言及しており、未開拓の分野や満たされていないニーズの評価も含まれています。最新の情報は2025年12月11日時点のものであり、市場の動向を把握するための貴重な洞察を提供しています。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

- 4.2 市場の推進要因

- 4.2.1 高性能コンピューティングとAIワークロードに対する需要の増加

- 4.2.2 データセンターの拡大による高帯域幅メモリの採用促進

- 4.2.3 スマートフォンおよび家電製品における急速な小型化

- 4.2.4 チップレットベースのヘテロジニアス統合アーキテクチャ

- 4.2.5 シリコンフォトニクスにおける3Dインターポーザスタッキングの必要性

- 4.2.6 先端パッケージング工場への政府補助金

- 4.3 市場の阻害要因

- 4.3.1 3D TSVパッケージの高いユニットコスト

- 4.3.2 熱に起因する信頼性と歩留まりの課題

- 4.3.3 TSVエッチングおよび充填ツールにおけるサプライチェーンのボトルネック

- 4.3.4 TSV化学物質に対するより厳格な環境規制

- 4.4 産業バリューチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

- 4.7 マクロ経済要因の影響

- 4.8 ポーターの5つの力分析

- 4.8.1 サプライヤーの交渉力

- 4.8.2 消費者の交渉力

- 4.8.3 新規参入の脅威

- 4.8.4 競争の激しさ

- 4.8.5 代替品の脅威

5. 市場規模と成長予測(金額)

- 5.1 製品タイプ別

- 5.1.1 イメージングおよび光電子

- 5.1.2 メモリ

- 5.1.3 MEMS / センサー

- 5.1.4 LED

- 5.1.5 その他の製品

- 5.2 TSV技術別

- 5.2.1 Via-Middle TSV

- 5.2.2 Via-Last TSV

- 5.2.3 Via-First TSV

- 5.3 ウェーハサイズ別

- 5.3.1 ≤200mm

- 5.3.2 300 mm

- 5.3.3 450 mm

- 5.4 エンドユーザー産業別

- 5.4.1 家庭用電化製品

- 5.4.2 自動車

- 5.4.3 ITおよび通信

- 5.4.4 ヘルスケア

- 5.4.5 航空宇宙および防衛

- 5.4.6 その他のエンドユーザー産業

- 5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米地域

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 スペイン

- 5.5.3.6 ロシア

- 5.5.3.7 その他のヨーロッパ地域

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 インド

- 5.5.4.4 韓国

- 5.5.4.5 オーストラリア

- 5.5.4.6 その他のアジア太平洋地域

- 5.5.5 中東およびアフリカ

- 5.5.5.1 中東

- 5.5.5.1.1 サウジアラビア

- 5.5.5.1.2 アラブ首長国連邦

- 5.5.5.1.3 トルコ

- 5.5.5.1.4 その他の中東地域

- 5.5.5.2 アフリカ

- 5.5.5.2.1 南アフリカ

- 5.5.5.2.2 ナイジェリア

- 5.5.5.2.3 エジプト

- 5.5.5.2.4 その他のアフリカ地域

6. 競争環境

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

- 6.4 企業プロファイル(グローバル概要、市場概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 Taiwan Semiconductor Manufacturing Company Limited

- 6.4.2 Samsung Electronics Co., Ltd.

- 6.4.3 Intel Corporation

- 6.4.4 Micron Technology, Inc.

- 6.4.5 SK hynix Inc.

- 6.4.6 Toshiba Electronic Devices and Storage Corporation

- 6.4.7 ASE Technology Holding Co., Ltd.

- 6.4.8 Amkor Technology, Inc.

- 6.4.9 United Microelectronics Corporation

- 6.4.10 STMicroelectronics N.V.

- 6.4.11 Broadcom Inc.

- 6.4.12 Texas Instruments Incorporated

- 6.4.13 GlobalFoundries Inc.

- 6.4.14 Advanced Micro Devices, Inc.

- 6.4.15 Qualcomm Incorporated

- 6.4.16 JCET Group Co., Ltd.

- 6.4.17 Powertech Technology Inc.

- 6.4.18 Siliconware Precision Industries Co., Ltd.

- 6.4.19 Xilinx, Inc. (AMD アダプティブおよび組み込みコンピューティンググループ)

- 6.4.20 Pure Storage, Inc.

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

3D TSVデバイスとは、半導体チップを垂直方向に積層し、シリコン貫通ビア(Through-Silicon Via: TSV)と呼ばれる微細な電気的接続で相互に接続した立体構造の半導体デバイスです。従来の2次元(2D)集積回路が平面配線に依存するのに対し、3D TSVはチップを重ねることで配線長を大幅に短縮し、多数の接続を実現します。TSVは、シリコンウェハやチップを垂直に貫通する導電性の経路で、通常は銅などで充填されます。この技術により、デバイスの小型化、高速化、低消費電力化、広帯域化が飛躍的に進展します。チップ間のデータ転送距離短縮は、信号遅延と消費電力の削減に大きく貢献し、ムーアの法則の限界に直面する現代半導体技術において、次世代性能向上を実現する重要な鍵となっています。

3D TSVデバイスの製造方法には、積層方式とTSV形成タイミングによる分類があります。積層方式では、「ウェハ・ツー・ウェハ(W2W)」積層は複数のウェハを丸ごと積層・接合し、高密度なTSV接続を大量生産するのに適しますが、歩留まり管理が課題です。「ダイ・ツー・ウェハ(D2W)」積層は、個々の良品チップ(KGD)をウェハ上に積層する方式で、異なるチップの混載や、良品のみを積層することで歩留まりを向上させやすい利点があります。さらに、「ダイ・ツー・ダイ(D2D)」積層は、個々のチップ同士を直接積層する方式で、最も柔軟性が高く、少量多品種生産やプロトタイピングに適しています。

TSV形成タイミングによる分類では、主に「ビア・ファースト(Via-First)」、「ビア・ミドル(Via-Middle)」、「ビア・ラスト(Via-Last)」の3つのアプローチがあります。ビア・ファーストは、トランジスタなどのデバイスが形成される前にTSVを形成する方法で、TSV形成時の熱的影響をデバイスに与えにくいという特徴があります。ビア・ミドルは、デバイス形成後、配線層が形成される前にTSVを形成する方法で、TSVの位置決め精度を確保しやすい利点があります。ビア・ラストは、全てのデバイスと配線層が完成した後にTSVを形成する方法で、既存の製造プロセスへの影響が少なく、最も後工程でTSVを導入できるため、柔軟性が高いとされています。

これらの製造技術の進化により、3D TSVデバイスは、高性能コンピューティング(HPC)、人工知能(AI)、データセンター、モバイルデバイスなど、幅広い分野での応用が期待されています。特に、メモリとプロセッサを近接して積層するHBM(High Bandwidth Memory)のような製品は、TSV技術の恩恵を最大限に活用し、データ転送速度とエネルギー効率を劇的に向上させています。今後も、TSV技術は半導体産業のイノベーションを牽引し、より高性能で効率的な電子デバイスの実現に不可欠な要素となるでしょう。