フィンフェット技術市場 規模・シェア分析:成長動向と予測(2025-2030年)

FinFETテクノロジー市場レポートは、テクノロジーノード(22nm、16/14nm、10nm、7nm、5nm以下)、ファウンドリビジネスモデル(ピュアプレイファウンドリ、IDM、ファブライト)、製品タイプ(CPU/MPU、GPU、SoC/アプリケーションプロセッサ、FPGA、ASIC/アクセラレータ、その他)、アプリケーション(スマートフォンおよびタブレット、ハイパフォーマンスコンピューティング/データセンターなど)、および地域別にセグメント化されています。市場予測は金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

FinFETテクノロジー市場の概要

本レポートは、FinFETテクノロジー市場の規模、シェア、成長トレンド、および2025年から2030年までの予測を詳細に分析しています。市場は、テクノロジーノード(22nm、16/14nm、10nm、7nm、5nm以下)、ファウンドリビジネスモデル(ピュアプレイファウンドリ、IDM、ファブライト)、製品タイプ(CPU/MPU、GPU、SoC/アプリケーションプロセッサ、FPGA、ASIC/アクセラレータなど)、アプリケーション(スマートフォンおよびタブレット、高性能コンピューティング/データセンターなど)、および地域別にセグメント化されています。市場予測は金額(米ドル)で提供されています。

市場規模と成長予測

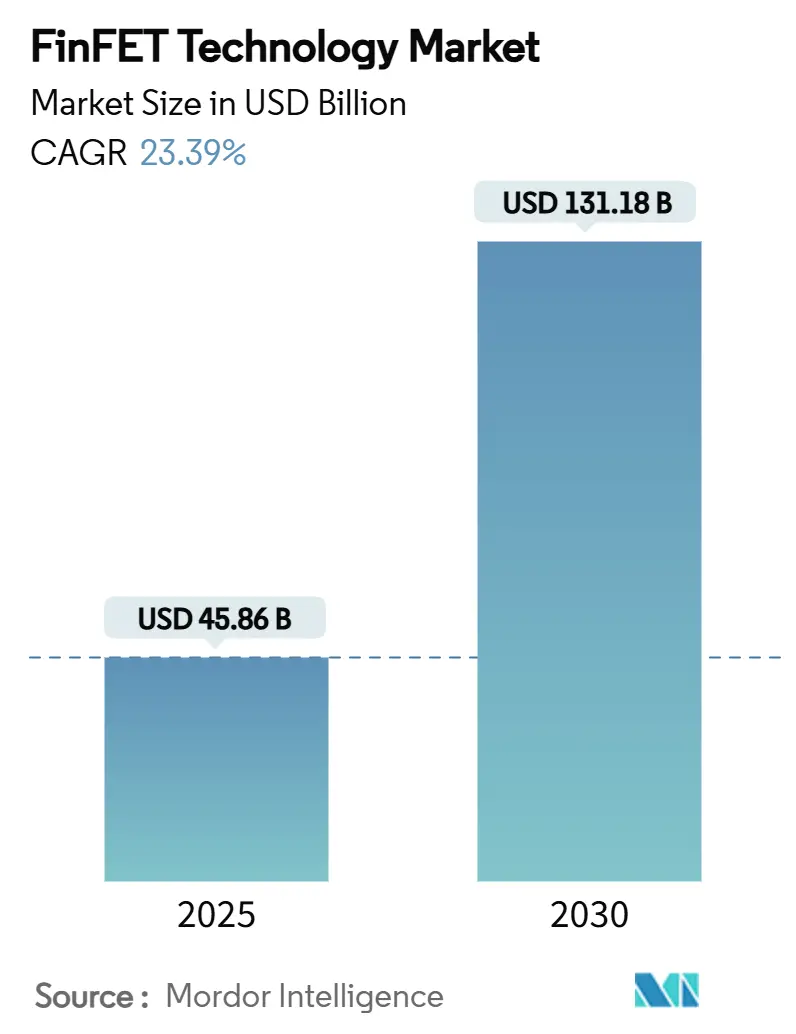

FinFETテクノロジー市場は、2025年には458.6億米ドルに達し、2030年には1,311.8億米ドルに成長すると予測されており、予測期間中の年平均成長率(CAGR)は23.39%と非常に高い伸びを示す見込みです。この急速な拡大は、半導体分野が20nm以下のプロセスでプレーナ型CMOSの限界に直面し、より高度なノードへの移行が進んでいることに起因しています。人工知能、5Gインフラ、電気自動車からのコンピューティング需要の激化により、FinFETデバイスが必要な電力性能バランスを提供するサブ5nmプロセスに資本が集中しています。米国および欧州連合における補助金に支えられた生産能力拡大は、FinFETテクノロジー市場の地理的フットプリントを再形成しており、最先端技術における継続的な歩留まりの課題は、製造成熟度の重要性を強調しています。同時に、3D-ICやチップレットアーキテクチャといったヘテロジニアス統合のトレンドは、高性能FinFETウェーハのダイレベルでの需要を増加させています。

主要な市場動向と洞察

市場成長の推進要因:

1. 5GおよびAIチップの爆発的な需要: 5G無線通信とクラウドAI推論エンジンの世界的な展開には、ワットあたりのスループットを最大化するロジックデバイスが不可欠です。FinFETプロセッサは、高性能グラフィックスユニット、専用AIアクセラレータ、カスタムクラウドASICにおいて優位性を確立しており、ハイパースケールオペレーターは容量確保のために複数年契約を結んでいます。大手ファウンドリは、サブ5nmラインの大部分をAI中心の設計に割り当てており、大規模言語モデルのワークロードの急速な採用が、より大きなダイサイズとトランジスタ数の増加を促しています。この結果、FinFETウェーハの需要は2027年まで加速すると予測されています。

2. 20nm以下のプレーナ型CMOSからの移行: 20nmノード以下では、短チャネル効果、オフ状態リーク、およびばらつきにより、2次元トランジスタの実用性が低下しました。FinFETのトライゲート構造は静電制御を回復させ、ゲート長の短縮とともに閾値電圧のスケーリングを可能にしました。2016年以降、ほぼすべての先進ロジックロードマップがFinFETに移行しており、FinFETは2026年まで量産の中核を担い続けると見られています。

3. 自動車ADASおよびEVコンピューティングの急増: ソフトウェア定義車両は、車載エレクトロニクスを分散型マイクロコントローラから、データセンターサーバーに匹敵する集中型ドメインコンピュータへと変革しています。レベル3以上の自動運転スタックには1,000 TOPSを超える処理能力が必要であり、高度なFinFET SoCと専用ニューラルネットワークアクセラレータが不可欠です。自動車の品質基準(AEC-Q100、ASIL-Dなど)は、信頼性が確立されたノード実績のあるFinFETプラットフォームを支持しています。

4. EU/米国CHIPS法による生産能力補助金: サプライチェーンの集中に対する国家的な懸念から、直接補助金、税額控除、融資保証を提供する産業政策が推進されています。米国は製造補助金に390億ドル、融資権限に750億ドルを割り当て、大手ファウンドリがアリゾナ、オハイオ、ニューヨークに複数の工場を建設するきっかけとなりました。欧州連合の430億ユーロのイニシアチブは、2030年までに世界の半導体製造シェアの20%を目標としており、自動車および産業用FinFETノードに焦点を当てた合弁事業を活性化させています。これらのインセンティブは、初期設備投資を削減し、FinFETテクノロジー市場を支えています。

5. 3D-ICおよび先進パッケージングの牽引: ヘテロジニアス統合、特に3D-ICおよびチップレットアーキテクチャのトレンドは、高性能FinFETウェーハのダイレベルでの需要を増加させています。

6. サブ5nmリーダーシップを巡るファウンドリ競争: 大手ファウンドリ間でのサブ5nmプロセスにおけるリーダーシップを巡る競争が激化しています。

市場成長の抑制要因:

1. サブ10nmプロセスの設備投資の増加(1工場あたり200億米ドル以上): グリーンフィールドのサブ5nm工場建設の総コストは、EUVスキャナーなどを含めると250億米ドルを超えます。減価償却費だけで完成ウェーハコストの55%以上を占めることがあり、新規参入企業の利益を圧迫し、競争の多様性をメガファウンドリの少数グループに限定しています。

2. EUVツール供給のボトルネック: 極端紫外線(EUV)スキャナーは、唯一のサプライヤーによる年間生産量が光学研磨、真空チャンバー加工、ペリクル供給によって制限されており、納期は18ヶ月以上に及んでいます。これにより、FinFETおよび今後のナノシートノードの生産能力増強が制約されています。

3. 設計ルールおよびEDAの複雑性の増大: 設計および電子設計自動化(EDA)の複雑性が高まっています。

4. マルチファウンドリフローにおける歩留まりのばらつき: 複数のファウンドリ間で一貫した歩留まりを維持することが課題となっています。

セグメント分析

* テクノロジーノード別: 2024年には7nmクラスがFinFETテクノロジー市場シェアの38.2%を占め、成熟度と性能のバランスが評価されています。一方、5nm以下のクラスは2030年までに24.2%のCAGRで最も急速に成長すると予測されており、クラウドプロバイダーや自動車メーカーが低消費電力のワークロードに移行していることが背景にあります。16/14nmはコスト重視のセグメントで、22nmは主にレガシーアプリケーションで需要があります。2nmノードではナノシートトランジスタが主流になりますが、FinFETは派生的な性能最適化バージョンとして共存すると見られています。

* ファウンドリビジネスモデル別: 2024年にはピュアプレイファウンドリが収益シェアの48.6%を占め、その規模の優位性、顧客中立性、R&Dへの集中が最先端のテープアウトにおいて選ばれる理由となっています。しかし、IDM(垂直統合型デバイスメーカー)セグメントは、垂直的な設計から製造までの制御と政府資金によって優先される安全な国内サプライチェーンを活用し、2030年までに25.4%のCAGRで最も急速に成長すると予測されています。

* 製品タイプ別: 2024年の収益の46.4%はSoC(システムオンチップ)およびアプリケーションプロセッサが占め、スマートフォンや家電製品の需要を反映しています。しかし、カスタムASIC/アクセラレータが最も急速に成長しており、ハイパースケールオペレーター、自動車メーカー、産業用OEMがドメイン固有のシリコン向けにワークロードを再設計しているため、25.6%のCAGRで増加すると予測されています。

* アプリケーション別: 2024年の出荷量の54.2%はスマートフォンおよびタブレットが占め、バッテリー寿命向上のためのFinFETへの依存が根強いことを示しています。高性能コンピューティング(HPC)およびデータセンターアクセラレータは、AI推論およびトレーニングクラスターの普及により、2030年までに24.3%のCAGRで最も急速に拡大するエンドマーケットとなっています。自動車エレクトロニクスも、インフォテインメントとADAS機能を統合した5nmまたは7nm FinFETプロセッサの採用により、急速に増加しています。

地域分析

* アジア太平洋地域: 2024年にはFinFETテクノロジー市場シェアの61.3%を占め、台湾の広範なファウンドリネットワーク、韓国のロジック・メモリ能力、中国の国内拡張に支えられています。この地域の23.8%という予測CAGRは、サブ5nmラインおよび先進パッケージング施設への継続的な設備投資を反映しています。

* 北米: CHIPS法によるインセンティブに牽引され、最も急速に成長している先進地域です。地域シェアは2024年の約10%から2030年代初頭には14%に上昇すると予測されています。

* 欧州: 430億ユーロの資金枠により戦略的自律性を追求しており、自動車および産業用FinFETノードに焦点を当てた合弁事業を誘致しています。

競争環境

FinFETテクノロジー市場は非常に集中しており、最大のピュアプレイファウンドリが先進ロジックウェーハ収益のほぼ3分の2を占めています。新規工場あたり200億米ドルを超える設備投資要件が新規参入を事実上不可能にし、寡占構造を強化しています。主要な競合他社は、プロセス設計の共同最適化、カスタマイズされたトランジスタライブラリ、およびロジックと高帯域幅メモリをバンドルする先進パッケージングロードマップを通じて差別化を図っています。政府のインセンティブも競争上の位置付けに影響を与えています。

主要企業:

TSMC Limited、Samsung Electronics Co., Ltd.、Intel Corporation、GlobalFoundries Inc.、Semiconductor Manufacturing International Corporation (SMIC)

最近の業界動向:

* 2025年7月: TSMCが2nmメモリチップ生産で90%の歩留まりを達成し、ナノシートの量産開始への道を開きました。

* 2025年7月: ASMLが初のHigh-NA EUV EXE:5200スキャナーをIntelに出荷し、2027年発売予定の14Åノード開発を開始しました。

* 2025年4月: TSMCが第2世代ナノシートとNanoFlex Proチャネルを特徴とするA14(1.4nmクラス)プラットフォームを発表し、2028年の量産を目指しています。

* 2025年4月: SynopsysとIntel Foundryが18Aおよび18A-Pプロセス向けのフルフローEDAサポートを開始し、リボンFETおよびバックサイドパワーノードへの顧客移行を効率化しました。

本レポートは、FinFET技術市場に関する包括的な分析を提供しています。市場の定義、調査方法、主要な調査結果、市場の動向、成長予測、競争環境、そして将来の展望について詳細に記述されています。

FinFET技術市場は、2030年までに1,311.8億米ドルに達すると予測されており、2025年の価値から約3倍に拡大する見込みです。2030年までの年平均成長率(CAGR)は23.39%と非常に高い成長が期待されています。

この急速な成長の主な要因としては、爆発的な5GおよびAIチップの需要、20nm以下のプレーナーCMOSからの移行、自動車のADAS(先進運転支援システム)およびEV(電気自動車)におけるコンピューティング需要の急増が挙げられます。これらの要因により、優れた電力効率と速度を提供するサブ5nm FinFETノードの採用が加速しています。また、3D-ICや先進パッケージング技術の牽引、そして5nm以下のプロセスにおけるファウンドリ間の競争も市場を活性化させています。

さらに、サブ5nmファブの建設には200億米ドルを超える巨額の設備投資が必要となるため、米国およびEUのCHIPS法に基づく補助金や税額控除が、地理的に分散された製造能力の確保と資本リスクの低減に重要な役割を果たしています。

市場は様々な側面から分析されています。

* 技術ノード別: 22nm、16/14nm、10nm、7nm、そして5nm以下に分類されます。現在、7nmファミリーが最大の収益シェアを占めていますが、AIおよびHPC(高性能コンピューティング)需要の加速に伴い、5nm以下のノードが24.2%のCAGRで最も速い成長を遂げると予測されています。

* ファウンドリビジネスモデル別: ピュアプレイファウンドリ、IDM(垂直統合型デバイスメーカー)、ファブライトモデルに分けられます。

* 製品タイプ別: CPU/MPU、GPU、SoC/アプリケーションプロセッサ、FPGA、ASIC/アクセラレータ、その他が含まれます。

* アプリケーション別: スマートフォンおよびタブレット、高性能コンピューティング/データセンター、車載エレクトロニクス、IoT/エッジデバイス、その他が主要な用途として挙げられます。

* 地域別: 北米、南米、ヨーロッパ、アジア太平洋(特に中国、日本、韓国、台湾)、中東およびアフリカといった広範な地域が対象となっています。

一方で、市場にはいくつかの制約も存在します。10nm以下のプロセスにおける設備投資の増加(1ファブあたり200億米ドル以上)、設計ルールとEDA(電子設計自動化)の複雑性の増大、EUV(極端紫外線)露光装置の供給ボトルネック、そして複数のファウンドリフローにおける歩留まりの変動などが挙げられます。

競争環境については、市場集中度、戦略的動向、市場シェア分析、および主要企業のプロファイルが詳細に調査されています。主要なプレーヤーとしては、台湾を拠点とする単一のピュアプレイファウンドリが先進ロジックの収益の約3分の2を占め、続いて韓国のコングロマリットと、積極的な生産能力増強を進める米国のIDMが挙げられます。具体的には、TSMC Limited、Samsung Electronics Co., Ltd.、Intel Corporation、GlobalFoundries Inc.、SMIC、UMCなどが主要企業として挙げられています。

FinFET技術の将来については、ゲートオールアラウンド(GAA)デバイスへの移行が注目されています。商用2nmナノシートの生産は2025年に開始される予定ですが、歩留まり、ツールの準備状況、IPエコシステムが収束するまでは、FinFETノードとGAAデバイスが共存すると予測されており、本格的なGAAへの移行は2027年以降になると見られています。

本レポートは、FinFET技術市場のあらゆる側面を網羅しており、市場の機会と将来の展望を明確に把握することが可能です。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

- 4.2 市場促進要因

- 4.2.1 5G/AIチップの爆発的な需要

- 4.2.2 20nm以下のプレーナーCMOSからの移行

- 4.2.3 車載ADASおよびEVコンピューティングの急増

- 4.2.4 EU/米国CHIPS法による生産能力補助金

- 4.2.5 3D-ICおよび先進パッケージングの牽引

- 4.2.6 5nm以下のリーダーシップを巡るファウンドリ競争

- 4.3 市場抑制要因

- 4.3.1 10nm以下の設備投資の増加(> 200億米ドル/工場)

- 4.3.2 設計ルールとEDAの複雑性の急増

- 4.3.3 EUVツールの供給ボトルネック

- 4.3.4 マルチファウンドリフローにおける歩留まりの変動

- 4.4 バリュー/サプライチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

- 4.7 ポーターの5つの力分析

- 4.7.1 新規参入者の脅威

- 4.7.2 買い手の交渉力

- 4.7.3 供給者の交渉力

- 4.7.4 代替品の脅威

- 4.7.5 競争上の対抗関係

5. 市場規模と成長予測(金額)

- 5.1 テクノロジーノード別

- 5.1.1 22 nm

- 5.1.2 16/14 nm

- 5.1.3 10 nm

- 5.1.4 7 nm

- 5.1.5 5 nm以下

- 5.2 ファウンドリビジネスモデル別

- 5.2.1 ピュアプレイファウンドリ

- 5.2.2 IDM

- 5.2.3 ファブライト

- 5.3 製品タイプ別

- 5.3.1 CPU / MPU

- 5.3.2 GPU

- 5.3.3 SoC / アプリケーションプロセッサ

- 5.3.4 FPGA

- 5.3.5 ASIC / アクセラレータ

- 5.3.6 その他

- 5.4 アプリケーション別

- 5.4.1 スマートフォンおよびタブレット

- 5.4.2 ハイパフォーマンスコンピューティング / データセンター

- 5.4.3 車載エレクトロニクス

- 5.4.4 IoT / エッジデバイス

- 5.4.5 その他

- 5.5 地域別

- 5.5.1 北米

- 5.5.1.1 アメリカ合衆国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米諸国

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 ロシア

- 5.5.3.6 スペイン

- 5.5.3.7 その他のヨーロッパ諸国

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 韓国

- 5.5.4.4 台湾

- 5.5.4.5 インド

- 5.5.4.6 その他のアジア太平洋諸国

- 5.5.5 中東およびアフリカ

- 5.5.5.1 中東

- 5.5.5.1.1 サウジアラビア

- 5.5.5.1.2 アラブ首長国連邦

- 5.5.5.1.3 トルコ

- 5.5.5.1.4 その他の中東諸国

- 5.5.5.2 アフリカ

- 5.5.5.2.1 南アフリカ

- 5.5.5.2.2 エジプト

- 5.5.5.2.3 その他のアフリカ諸国

6. 競争環境

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

- 6.4 企業プロファイル(グローバルレベルの概要、市場レベルの概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 TSMC Limited

- 6.4.2 Samsung Electronics Co., Ltd.

- 6.4.3 Intel Corporation

- 6.4.4 GlobalFoundries Inc.

- 6.4.5 Semiconductor Manufacturing International Corporation (SMIC)

- 6.4.6 United Microelectronics Corporation (UMC)

- 6.4.7 IBM Corporation

- 6.4.8 Arm Holdings plc

- 6.4.9 Qualcomm Incorporated

- 6.4.10 NVIDIA Corporation

- 6.4.11 AMD Corporation

- 6.4.12 Broadcom Inc.

- 6.4.13 Apple Inc.

- 6.4.14 MediaTek Inc.

- 6.4.15 NXP Semiconductors N.V.

- 6.4.16 Marvell Technology Inc.

- 6.4.17 Synopsys Inc.

- 6.4.18 Cadence Design Systems Inc.

- 6.4.19 ASE Technology Co. Ltd.

- 6.4.20 Amkor Technology Inc.

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

フィンフェット技術は、半導体集積回路におけるトランジスタの基本的な構造を革新した画期的な技術でございます。その正式名称は「Fin Field-Effect Transistor(フィン電界効果トランジスタ)」であり、従来のプレーナー型(平面型)MOSFETが抱えていた微細化の限界を克服するために開発されました。この技術は、トランジスタのチャネル部分を魚の「ひれ(fin)」のような立体的な構造にすることで、ゲートがチャネルを複数方向から取り囲むことを可能にしています。これにより、ゲートによるチャネルの制御性が大幅に向上し、リーク電流の抑制とスイッチング速度の向上が実現されました。

従来のプレーナー型トランジスタでは、ゲートはチャネルの上部にのみ配置されていました。しかし、トランジスタが微細化されるにつれて、ゲートがチャネルを十分に制御できなくなり、「ショートチャネル効果」と呼ばれる現象が発生しやすくなりました。これは、トランジスタがオフの状態でも電流が漏れ出す(リーク電流)原因となり、消費電力の増大や性能の低下を招きます。フィンフェット技術は、ゲートがチャネルの側面と上部(通常は三方向)からチャネルを包み込む「マルチゲート構造」を採用することで、この問題を根本的に解決しました。結果として、トランジスタのオン/オフ制御がより正確になり、低消費電力と高性能を両立させることが可能になったのです。

フィンフェット技術自体には、基本的な構造原理において大きな「種類」の分類があるわけではありませんが、その実装や設計においては様々な最適化が図られてきました。例えば、駆動電流を増やすために複数のフィンを並列に配置する「マルチフィン構造」や、フィンの高さや幅、ゲート材料の選択など、製造プロセスや性能要件に応じて細かな設計変更が行われています。インテル社が22nmプロセスで初めて「トライゲートトランジスタ」として導入して以来、TSMC、サムスン、グローバルファウンドリーズといった主要な半導体ファウンドリー各社が、それぞれ独自のプロセス技術と最適化を施したフィンフェットを開発・採用してまいりました。

フィンフェット技術の進化の方向性としては、さらにゲートによるチャネル制御を強化する「ゲート・オール・アラウンド(GAA)FET」への移行が挙げられます。GAAFETは、フィンフェットのチャネルが「ひれ」状であるのに対し、チャネルをナノシートやナノワイヤーといった完全にゲートが取り囲む構造にすることで、四方からのゲート制御を実現します。これは、フィンフェットの究極的な進化形とも言えるもので、3nm以降のさらなる微細化ノードにおいて、フィンフェットの限界を突破する次世代技術として注目されています。GAAFETは、フィンフェットの基本的な思想である「立体構造によるゲート制御の強化」をさらに推し進めたものと言えるでしょう。

フィンフェット技術は、その優れた性能と電力効率から、現代の高性能半導体製品のほとんどに採用されています。主な用途としては、まず、パソコンやサーバーのCPU(中央演算処理装置)、グラフィックス処理を担うGPU(画像処理装置)、そして近年需要が高まっているAIアクセラレータなど、膨大な計算能力を必要とする高性能プロセッサの中核をなしています。フィンフェットは、これらのプロセッサがより多くのトランジスタを搭載し、かつ高速で動作しながらも消費電力を抑えることを可能にしました。

次に、スマートフォンやタブレット向けのSoC(System-on-Chip)です。これらのモバイルデバイスでは、限られたバッテリー容量で長時間動作させる必要があるため、低消費電力は極めて重要な要素です。フィンフェット技術は、高性能なアプリケーションプロセッサや通信モデムなどを統合したSoCにおいて、高い処理能力と優れた電力効率の両立を実現し、スマートフォンの進化を支えてきました。さらに、データセンターのサーバー、ネットワーク機器、自動車の先進運転支援システム(ADAS)やインフォテインメントシステムなど、幅広い分野でフィンフェット技術が活用されています。これらの用途では、信頼性、処理能力、そして電力効率が非常に重視されるため、フィンフェットの特性が最大限に生かされています。22nm、16nm/14nm、10nm、7nm、5nm、そして一部の3nmプロセスに至るまで、フィンフェットは最先端の半導体製造技術のデファクトスタンダードとして君臨してまいりました。

フィンフェット技術の登場と普及は、他の多くの半導体製造技術の進化と密接に関連しています。まず、フィンフェットの前身として、従来のプレーナー型MOSFETが挙げられます。フィンフェットは、プレーナー型トランジスタが微細化の限界に直面した際に、その課題を解決するために開発されました。プレーナー型では、ゲートがチャネルを上からしか制御できないため、28nmノードあたりからショートチャネル効果が顕著になり、リーク電流の増大が問題となりました。フィンフェットは、この問題を立体構造で解決したのです。

次に、フィンフェットの後継技術として、前述のゲート・オール・アラウンド(GAA)FET、特にナノシートFETやナノワイヤーFETが挙げられます。フィンフェットもさらなる微細化には限界があり、特にチャネル幅の制御や静電的な完全制御が難しくなってきます。GAAFETは、チャネルを完全にゲートで囲むことで、フィンフェットよりもさらに優れた静電制御を実現し、3nm以降の超微細化ノードで採用が進んでいます。また、フィンフェットの製造には、極めて高度な製造技術が不可欠です。例えば、微細なフィン構造を形成するためのEUV(極端紫外線)リソグラフィや、原子レベルで薄膜を堆積させるALD(原子層堆積)技術、そして精密なエッチング技術などが挙げられます。さらに、ゲート絶縁膜に高誘電率材料を用いるHigh-kメタルゲート(HKMG)技術も、フィンフェットと組み合わせて使用されることで、ゲートリーク電流のさらなる低減と性能向上に貢献しています。

フィンフェット技術は、ムーアの法則の継続を可能にした最も重要な技術革新の一つとして、半導体産業に計り知れない影響を与えました。2000年代後半、従来のプレーナー型トランジスタは、28nmプロセスノードあたりで物理的な限界に直面し始めていました。トランジスタをさらに小さくすると、ゲートがチャネルを十分に制御できなくなり、オフ状態でも電流が漏れ出す「リーク電流」が増大し、消費電力の増加や発熱の問題が深刻化していたのです。このままでは、半導体の性能向上と電力効率改善という、ムーアの法則が示唆する進化が停滞する危機に瀕していました。

このような背景の中、インテル社が2011年に22nmプロセスで「トライゲートトランジスタ」としてフィンフェット技術を世界で初めて量産適用しました。これは、半導体業界全体に大きな衝撃を与え、その後の技術ロードマップを大きく変えることになりました。他の主要ファウンドリーも追随し、16nm/14nmプロセスノードからフィンフェット技術を導入しました。この技術の採用により、トランジスタの微細化はさらに進み、7nm、5nm、そして一部の3nmプロセスへと到達することができました。フィンフェットは、高性能コンピューティング、モバイルデバイス、AI、データセンターなど、現代社会を支えるあらゆるデジタル技術の進化を可能にしました。消費電力を抑えながら、より多くのトランジスタを搭載し、より高速に動作するチップを製造できるようになったことで、スマートフォンの高性能化、クラウドサービスの拡大、AI技術の発展など、過去10年間の技術革新の多くはフィンフェット技術の恩恵を受けていると言っても過言ではありません。フィンフェットは、半導体産業における競争力を維持し、デジタル社会の発展を加速させる上で不可欠な基盤技術となったのです。

フィンフェット技術は、長らく半導体微細化の主役を担ってきましたが、その進化にも物理的な限界が見え始めています。フィン構造をさらに微細化し、高さを増していくと、製造プロセスの複雑性が増大し、コストや歩留まりの課題が顕著になります。また、極限まで微細化されたフィンでは、ゲートによるチャネルの静電制御が再び難しくなり、リーク電流の抑制や性能向上が頭打ちになる可能性が指摘されています。

このような背景から、半導体業界はフィンフェットの次の世代のトランジスタ技術へと移行を進めています。その最たるものが、前述のゲート・オール・アラウンド(GAA)FET、特にナノシートFETやナノワイヤーFETです。GAAFETは、チャネルを完全にゲートで囲むことで、フィンフェットよりもさらに優れた静電制御を実現し、3nm以降の超微細化ノードで採用が本格化しています。サムスン電子は3nmプロセスでGAAFET(MBCFETと呼称)を導入し、インテルも「RibbonFET」としてGAAFETの採用を計画しており、TSMCも将来的なナノシートFETの導入を視野に入れています。GAAFETへの移行は、フィンフェットが確立した3D構造によるゲート制御の思想をさらに発展させたものであり、フィンフェット技術が培ってきた製造技術や設計ノウハウが基盤となっています。将来的には、GAAFETのさらに先を行くCFET(Complementary FET)や、2次元材料(グラフェン、MoS2など)を用いたトランジスタ、カーボンナノチューブトランジスタ、さらには量子コンピューティングといった全く新しい計算パラダイムの研究も進められています。フィンフェット技術は、半導体微細化の歴史において重要なマイルストーンであり、その原理と課題解決のアプローチは、今後のトランジスタ技術の発展においても引き続き重要な示唆を与え続けるでしょう。