3D TSVおよび2.5D市場 規模・シェア分析 – 成長動向・予測 (2025-2030年)

グローバル3D TSVおよび2.5D市場は、パッケージングタイプ(3D積層メモリ、2.5Dインターポーザー、TSV搭載CIS、3D SoC)、エンドユーザーアプリケーション(家電、自動車、ハイパフォーマンスコンピューティング(HPC)、ネットワーキング)、および地域(北米、欧州、アジア太平洋、その他地域)によってセグメント化されています。上記すべてのセグメントについて、市場規模と予測は米ドル(USD)での価値で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

「3D TSVおよび2.5D市場:規模、シェア、業界分析」

この市場調査レポートは、3D TSV(Through Silicon Via)および2.5D市場の現状と将来予測について詳細に分析しています。調査期間は2019年から2030年で、市場はパッケージングタイプ(3D積層メモリ、2.5Dインターポーザー、TSV搭載CIS、3D SoC)、最終用途アプリケーション(家電、自動車、高性能コンピューティング(HPC)、ネットワーキング)、および地域(北米、欧州、アジア太平洋、その他地域)に分類されています。市場規模は米ドル建てで提供されています。

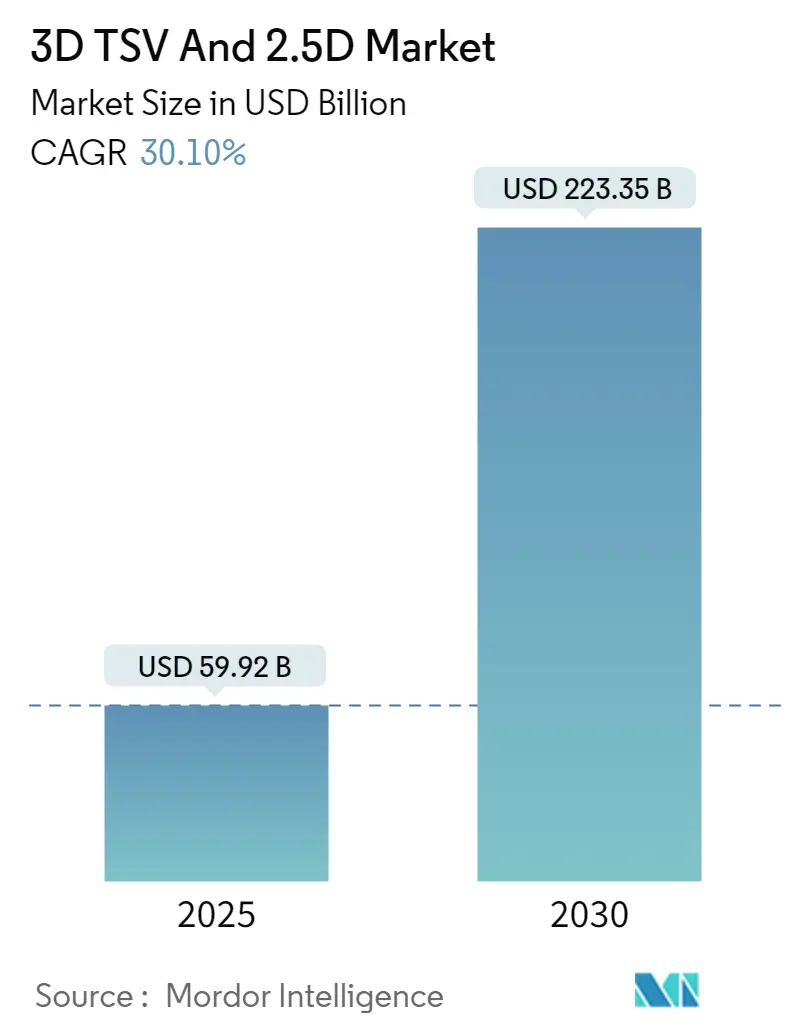

2025年には599.2億米ドルと推定されるこの市場は、2030年までに2233.5億米ドルに達すると予測されており、予測期間(2025年~2030年)における年平均成長率(CAGR)は30.1%と非常に高い成長が見込まれています。最も急速に成長する市場はアジア太平洋地域であり、最大の市場は北米です。市場の集中度は低いとされています。主要なプレーヤーには、東芝、サムスン電子、ASEグループ、台湾積体電路製造(TSMC)、アムコーテクノロジーなどが挙げられます。

市場概要

半導体業界におけるパッケージング技術は、継続的な変革を遂げています。CMOSスケーリングの鈍化とコスト上昇により、業界はICパッケージングの進化に依存せざるを得なくなっています。3Dスタッキング技術は、AI、機械学習(ML)、データセンターなどのアプリケーションに必要な性能を満たすソリューションとして注目されています。特に、高性能コンピューティング(HPC)アプリケーションへの需要の高まりが、TSV市場を牽引する主要な要因となっています。

3D TSVパッケージング技術は、チップ間のデータ伝送時間を短縮し、従来のワイヤーボンディング技術と比較して消費電力を大幅に削減し、高速化を実現します。2022年10月には、TSMCが次世代HPCおよびモバイル技術の迅速な統合を支援するため、革新的な3DFabric Allianceを発表しました。これは、半導体およびシステムレベルの設計課題を克服するための重要な取り組みです。

消費者の電子機器に対する需要の増加は、多様な新機能を実現する高度な半導体デバイスの必要性を高めています。半導体アプライアンスの需要が継続的に高まる中、先進的なパッケージング技術は、今日のデジタル化された世界に必要なフォームファクターと処理能力を提供しています。例えば、半導体工業会によると、2022年8月の世界の半導体産業の売上高は474億米ドルで、2021年8月と比較して0.1%のわずかな増加でした。

また、GSMアソシエーションによると、2025年までに米国は世界で最も高いスマートフォン普及率(接続数の49%)を達成すると予測されています。米国IoTアソシエーションによれば、米国は世帯あたりのスマートホームデバイス比率が最も高く、2つまたは3つのユースケース(エネルギー、セキュリティ、家電)でアプライアンスを所有する消費者の傾向が最も顕著です。

さらに、2022年9月には、バイデン政権が中国への依存に対抗するため、国内半導体産業の構築に500億米ドルを投資すると発表しました。米国は国家安全保障に不可欠な最先端チップの25%を消費する一方で、生産はゼロであるためです。2022年8月には、ジョー・バイデン大統領が国内のハイテク製造業を強化するための2800億米ドルのCHIPS法に署名しました。このような半導体分野への強力な投資は、本市場の成長に有利な機会をもたらすでしょう。

MEMS(微小電気機械システム)およびセンサーの成長は、自動車、産業オートメーションなど、さまざまなアプリケーションにおけるセンサーとディスプレイの需要が急速に増加していることに起因しています。2022年8月、MEMSメーカーであり世界の半導体産業の主要プレーヤーであるSTマイクロエレクトロニクスは、消費者向けスマート産業、モバイルデバイス、ヘルスケア、小売分野向けに設計された第3世代MEMSセンサーを発表しました。これらの堅牢なチップサイズのモーションセンサーと環境センサーは、今日のスマートフォンやウェアラブルのユーザーフレンドリーでコンテキスト認識機能を実現しており、MEMS技術に基づいて製造されています。STの最新MEMSセンサー世代は、出力精度と消費電力の点で技術的限界を押し広げ、性能を新たなレベルに引き上げています。

一方で、TSVデバイス製造に関連する高コストが市場成長を抑制しています。これには、デバイス自体のコストだけでなく、適切な機能に必要なアクセサリーや消耗品のコストも含まれます。さらに、TSVデバイス製造を管理する厳格なガイドラインや規制もコストを増加させる要因となっています。

世界的な半導体不足は、パンデミック後、各プレーヤーに生産能力の拡大を促しました。例えば、SMICは2025年までに異なる都市に新しいチップ製造工場を建設することで、生産能力を倍増させる積極的な計画を発表しました。また、多くのアジア太平洋地域の地方政府は、長期プログラムで半導体産業に資金を投入しており、市場の成長を回復させると期待されています。例えば、中国政府は「国家IC投資基金2030」の第2段階に約230億~300億米ドルを投入しました。

さらに、ロシアとウクライナ間の紛争は、エレクトロニクス産業に大きな影響を与えると予想されています。この紛争は、以前から業界を悩ませていた半導体サプライチェーンの問題とチップ不足をさらに悪化させました。ニッケル、パラジウム、銅、チタン、アルミニウム、鉄鉱石などの重要な原材料の価格変動という形で混乱が生じ、材料不足につながる可能性があります。これは、3D積層メモリの製造を妨げるでしょう。

主要な市場トレンドと洞察

LEDパッケージングが著しい成長を遂げると予測

製品におけるLEDの使用増加は、より高出力、高密度、低コストのデバイスの拡大を促進しています。シリコン貫通ビア(TSV)技術を用いた3次元(3D)パッケージングは、2Dパッケージングとは異なり、高密度の垂直相互接続を可能にします。TSV集積回路は接続長を短縮するため、モノリシック統合と多機能統合が効率的に行われる場所で、より小さな寄生容量、インダクタンス、抵抗が必要とされ、高速で低電力の相互接続を提供します。国際エネルギー機関(IEA)によると、国際照明市場におけるLEDの普及率は、2025年には約76%、2030年には87.4%に達すると予測されています。

エネルギー効率の高いLEDの採用を促す政府のイニシアチブや規制も、本市場を牽引しています。米国エネルギー省は最近、数千の家庭や企業を最先端のエネルギー効率の高いネットワークに変えるための最新技術を用いた10のパイロットプロジェクトに6100万米ドルを投資すると発表しました。これは、白熱電球やハロゲン電球をよりエネルギー効率の高いLED照明に切り替えることに適用されます。その結果、LEDの拡大に伴い、予測期間中に米国におけるLEDパッケージングの需要が増加するでしょう。

市場の様々なプレーヤーが新製品を開発しており、2022年5月にはLumileds LLCが高出力CSP(チップスケールパッケージ)LEDを発表しました。LEDパッケージアプリケーションの急速な進歩は、今後数年間でイノベーションと消費を増加させ、本市場の成長を推進すると予測されています。

アジア太平洋地域が市場で大きなシェアを占めると予測

アジア太平洋地域は、本市場において最も成長している地域です。スマートフォンの普及率の上昇は、主に人口増加と都市化により、この地域を世界有数のモバイル市場の一つにしました。GSMアソシエーションによると、アジア太平洋地域の人口の96%がスマートフォンブロードバンドネットワークにカバーされており、12億人がモバイルインターネットサービスにアクセスしています。5Gの勢いは地域全体で加速しており、2025年までにこの地域全体で4億の5G接続があると予測されています。さらに、インダストリー4.0もアジア太平洋地域で最も台頭しているトレンドの一つであり、IoTデバイスと小型化は3D TSVを活用しています。

中国工業情報化部(MIIT)によると、中国本土には現在142.5万の5G基地局が設置されており、全国で5億人以上の5Gユーザーをサポートしており、世界で最も広範なネットワークとなっています。この地域での5Gの導入拡大は、5G対応デバイスの需要を促進し、市場の成長をさらに加速させるでしょう。

このレポートは、「グローバル3D TSVおよび2.5D市場」に関する包括的な分析を提供しています。TSV(Through-Silicon Via)は、シリコンウェハーを垂直に貫通する高性能な相互接続技術であり、消費電力の削減と電気的性能の向上を実現します。本調査は、この技術を用いた市場の現状、将来予測、主要な動向を詳細に評価しています。

市場は、主に以下の要素で細分化されています。

* パッケージングタイプ別: 3D積層メモリ、2.5Dインターポーザー、TSV搭載CIS(CMOSイメージセンサー)、3D SoC、その他(LED、MEMS&センサーなど)が含まれます。

* エンドユーザーアプリケーション別: 消費者向け電子機器、自動車、高性能コンピューティング(HPC)およびネットワーキング、その他のアプリケーションが対象です。

* 地域別: 北米(米国、カナダ)、欧州(英国、ドイツ、フランス、イタリア、その他欧州)、アジア太平洋(中国、インド、日本、オーストラリア、東南アジア、その他アジア太平洋)、およびその他の地域に分類されています。

調査は厳格な方法論に基づいて実施されており、市場の仮定と定義が明確にされています。市場の魅力度を評価するためにポーターのファイブフォース分析(サプライヤーの交渉力、バイヤーの交渉力、新規参入の脅威、代替品の脅威、競争の激しさ)が用いられ、業界のバリューチェーン分析やマクロ経済トレンドが市場に与える影響も詳細に分析されています。

市場の成長を牽引する主要な要因としては、高性能コンピューティング(HPC)アプリケーション市場の拡大、およびデータセンターとメモリデバイスの適用範囲の拡大が挙げられます。一方で、ICパッケージのユニットコストが高いことが、市場の課題として認識されています。

市場規模と予測に関して、重要なデータが示されています。2024年の市場規模は418.8億米ドルと推定されており、2025年には599.2億米ドルに達すると予測されています。さらに、2025年から2030年にかけて年平均成長率(CAGR)30.10%で成長し、2030年には2233.5億米ドルに達すると見込まれています。

地域別では、2025年には北米が最大の市場シェアを占めると予測されています。また、アジア太平洋地域は、予測期間(2025年~2030年)において最も高いCAGRで成長すると推定されており、今後の市場拡大の主要な牽引役となることが期待されます。

競争環境の分析では、東芝、サムスン電子、ASEグループ、台湾積体電路製造(TSMC)、アムコー・テクノロジー、ピュア・ストレージ、ユナイテッド・マイクロエレクトロニクス、STマイクロエレクトロニクス、ブロードコム、インテル、江蘇長電科技などの主要企業が挙げられています。これらの企業は、市場における主要なプレーヤーとして活動しています。

本レポートでは、上記の他に、技術スナップショット、投資分析、および市場の将来に関する展望も含まれており、市場の全体像を深く理解するための情報が提供されています。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場の洞察

- 4.1 市場概要

-

4.2 業界の魅力度 – ポーターの5つの力分析

- 4.2.1 供給者の交渉力

- 4.2.2 買い手の交渉力

- 4.2.3 新規参入の脅威

- 4.2.4 代替品の脅威

- 4.2.5 競争の激しさ

- 4.3 業界のバリューチェーン分析

- 4.4 マクロ経済動向が市場に与える影響

5. 市場のダイナミクス

-

5.1 市場の推進要因

- 5.1.1 ハイパフォーマンスコンピューティングアプリケーション市場の拡大

- 5.1.2 データセンターとメモリデバイスの範囲拡大

-

5.2 市場の課題

- 5.2.1 ICパッケージの単位コストの高さ

6. 技術概要

7. 市場セグメンテーション

-

7.1 パッケージングタイプ別

- 7.1.1 3D積層メモリ

- 7.1.2 2.5Dインターポーザー

- 7.1.3 TSV搭載CIS

- 7.1.4 3D SoC

- 7.1.5 その他のパッケージングタイプ(LED、MEMS & センサーなど)

-

7.2 エンドユーザーアプリケーション別

- 7.2.1 家庭用電化製品

- 7.2.2 自動車

- 7.2.3 ハイパフォーマンスコンピューティング(HPC)およびネットワーキング

- 7.2.4 その他のエンドユーザーアプリケーション

-

7.3 地域別

- 7.3.1 北米

- 7.3.1.1 米国

- 7.3.1.2 カナダ

- 7.3.2 ヨーロッパ

- 7.3.2.1 イギリス

- 7.3.2.2 ドイツ

- 7.3.2.3 フランス

- 7.3.2.4 イタリア

- 7.3.2.5 その他のヨーロッパ

- 7.3.3 アジア太平洋

- 7.3.3.1 中国

- 7.3.3.2 インド

- 7.3.3.3 日本

- 7.3.3.4 オーストラリア

- 7.3.3.5 東南アジア

- 7.3.3.6 その他のアジア太平洋

- 7.3.4 その他の地域

8. 競争環境

-

8.1 企業プロフィール

- 8.1.1 東芝株式会社

- 8.1.2 サムスン電子株式会社

- 8.1.3 ASEグループ

- 8.1.4 台湾積体電路製造株式会社

- 8.1.5 アンコール・テクノロジー株式会社

- 8.1.6 ピュア・ストレージ株式会社

- 8.1.7 ユナイテッド・マイクロエレクトロニクス株式会社

- 8.1.8 STマイクロエレクトロニクスNV

- 8.1.9 ブロードコム株式会社

- 8.1.10 インテル株式会社

- 8.1.11 江蘇長電科技株式会社

- *リストは網羅的ではありません

9. 投資分析

10. 市場の将来

*** 本調査レポートに関するお問い合わせ ***

半導体技術の進化は、長らく微細化によって駆動されてきましたが、物理的な限界と製造コストの増大により、そのペースは鈍化しつつあります。このような背景の中で、半導体チップの性能向上、小型化、省電力化を実現する新たなアプローチとして、2.5Dおよび3D TSV(Through-Silicon Via)技術が極めて重要な役割を担っています。これらの技術は、複数の半導体チップを垂直方向または水平方向に高密度に集積することで、従来の2次元集積回路の限界を打破し、次世代の電子機器の基盤を築いています。

まず、これらの技術の定義についてご説明いたします。2.5D集積技術とは、複数の半導体チップ(ダイ)を、シリコンインターポーザと呼ばれる中間基板上に水平に配置し、インターポーザを介して高密度に接続する技術です。このインターポーザ自体には、パッケージ基板との接続のためにTSVが用いられます。これにより、チップ間の配線長を大幅に短縮し、高速かつ広帯域なデータ転送を可能にします。一方、3D TSV技術は、シリコンウェーハまたはダイを垂直に貫通する電気的接続(ビア)を形成する技術そのものを指します。このTSVが、複数のチップを垂直に積層する3D集積化の基盤となります。そして、3D集積技術とは、このTSVを用いて複数の半導体チップを垂直に積層し、直接電気的に接続する技術です。これにより、チップ間の配線長が極めて短くなり、超高速・超広帯域なデータ転送、大幅な小型化、そして低消費電力化が実現されます。

次に、これらの技術の種類について見ていきましょう。2.5D集積におけるインターポーザには、最も一般的で高密度配線とTSV形成が可能なシリコンインターポーザのほか、コストを抑えられる有機インターポーザ、そして優れた電気特性が期待される新興のガラスインターポーザなどがあります。3D TSVを用いた積層方式には、ウェーハを丸ごと積層・接合し、その後ダイシングするウェーハ・ツー・ウェーハ(W2W)方式、個々の良品ダイ(KGD: Known Good Die)をウェーハ上に積層するダイ・ツー・ウェーハ(D2W)方式、そして個々のKGDを別の個々のKGD上に積層するダイ・ツー・ダイ(D2D)方式があります。それぞれ生産性、柔軟性、歩留まり管理の面で異なる特徴を持ちます。また、TSVの形成タイミングによっても、トランジスタ形成前のビアファースト、トランジスタ形成後のビアミドル、全てのプロセス完了後のビアラストといった種類があり、それぞれプロセス上の利点と課題が存在します。

これらの技術は多岐にわたる分野で活用されています。最も顕著な用途の一つは、高性能コンピューティング(HPC)分野です。CPU、GPU、AIアクセラレータ、データセンター向けプロセッサなどでは、HBM(High Bandwidth Memory)と組み合わせた2.5D集積が広く採用されています。HBMはTSVを用いた3D積層メモリの代表例であり、プロセッサとメモリ間のボトルネックを解消し、飛躍的な性能向上に貢献しています。また、モバイル機器では、CMOSイメージセンサーにおいて画素部とロジック部を3D積層することで、高性能化と小型化を実現しています。一部のモバイルメモリ(LPDDR)でもTSVが活用され、ネットワーク機器や車載システム、さらには小型・低消費電力化が求められるIoTデバイスなど、幅広い分野での応用が進んでいます。

2.5Dおよび3D TSV技術の実現には、様々な関連技術が不可欠です。積層されたチップやインターポーザを電気的に接続するためのマイクロバンプや、より微細なピッチと高密度接続を可能にするハイブリッドボンディング(銅-銅直接接合)は、今後の3D集積の鍵となる技術です。また、高集積化による発熱密度の増大に対応するため、マイクロ流体冷却や高度なヒートシンクなど、効率的な熱管理技術が不可欠です。積層する個々のダイが確実に良品であることを保証するKGD技術は、3D集積の歩留まり向上に極めて重要であり、複雑な3D構造のテストを容易にするためのテスト容易化設計(DfT)も欠かせません。さらに、積層のためにウェーハを極限まで薄くするウェーハ薄化技術や、それを破損なく扱うハンドリング技術、そして2.5D/3D積層されたチップを最終的なパッケージに収めるための高度なパッケージング技術も重要な要素です。

これらの技術が注目される市場背景には、いくつかの要因があります。まず、従来の微細化による性能向上が物理的・経済的に困難になる中で、2.5Dおよび3D集積は「More than Moore」の方向性として、性能向上と機能集積の新たな道を開いています。AI、機械学習、ビッグデータ処理、HPCといった分野では、膨大なデータ処理能力とメモリ帯域幅が不可欠であり、これらの技術がその要求に応えます。また、モバイル機器やIoTデバイスの普及により、より小型で消費電力の低い半導体デバイスへの需要が高まっており、3D集積はそのニーズに合致します。さらに、異なるプロセスで製造された多様な機能(ロジック、メモリ、アナログ、RFなど)を持つチップを一つのパッケージに統合するヘテロジニアス集積のニーズが高まっており、2.5D/3D技術はその実現に不可欠な基盤技術となっています。

将来展望としては、2.5Dおよび3D TSV技術は、現在HPCやハイエンドメモリが中心ですが、今後はより幅広いアプリケーションでの採用が進むと予想されます。特に、ハイブリッドボンディングは、より微細なピッチと高い接続信頼性を持つことで、3D集積の標準技術となることが期待され、チップレット間の接続密度を飛躍的に向上させるでしょう。この技術は、異なるベンダーが製造した専門性の高いチップレットを組み合わせて一つの高性能なシステムを構築するチップレットエコシステムの発展を加速させます。また、現在の3D集積がダイ間の接続であるのに対し、単一のウェーハ内で複数のアクティブデバイス層を直接積層するモノリシック3D集積の研究も進められており、さらなる高密度化と性能向上が期待されます。電気信号の代わりに光信号を用いる光TSVの研究も進んでおり、将来的に超広帯域・低消費電力なチップ間通信を実現する可能性があります。設計、テスト、製造プロセスにおいてAIや機械学習を活用することで、3D集積回路の複雑な課題を解決し、開発期間の短縮と歩留まり向上に貢献すると考えられます。さらに、異なるベンダー間の相互運用性を確保するため、インターフェースやテスト方法の標準化が今後も進められていくでしょう。これらの技術は、半導体産業の未来を形作る上で不可欠な要素であり、その進化は今後も私たちの生活に大きな影響を与え続けることになります。