ゲートオールアラウンドFET市場規模・シェア分析 – 成長トレンドと予測 (2025-2030年)

ゲートオールアラウンドFET市場レポートは、トランジスタアーキテクチャ(ナノシートGAAFET、ナノワイヤGAAFET、フォークシートFET)、ウェーハサイズ(300mm、200mm、150mm未満)、アプリケーション(スマートフォンおよびモバイルデバイス、高性能コンピューティングおよびデータセンターなど)、エンドユーザー産業(ファウンドリ、IDM、ファブレスIC設計者など)、および地域によって分類されます。市場予測は、金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

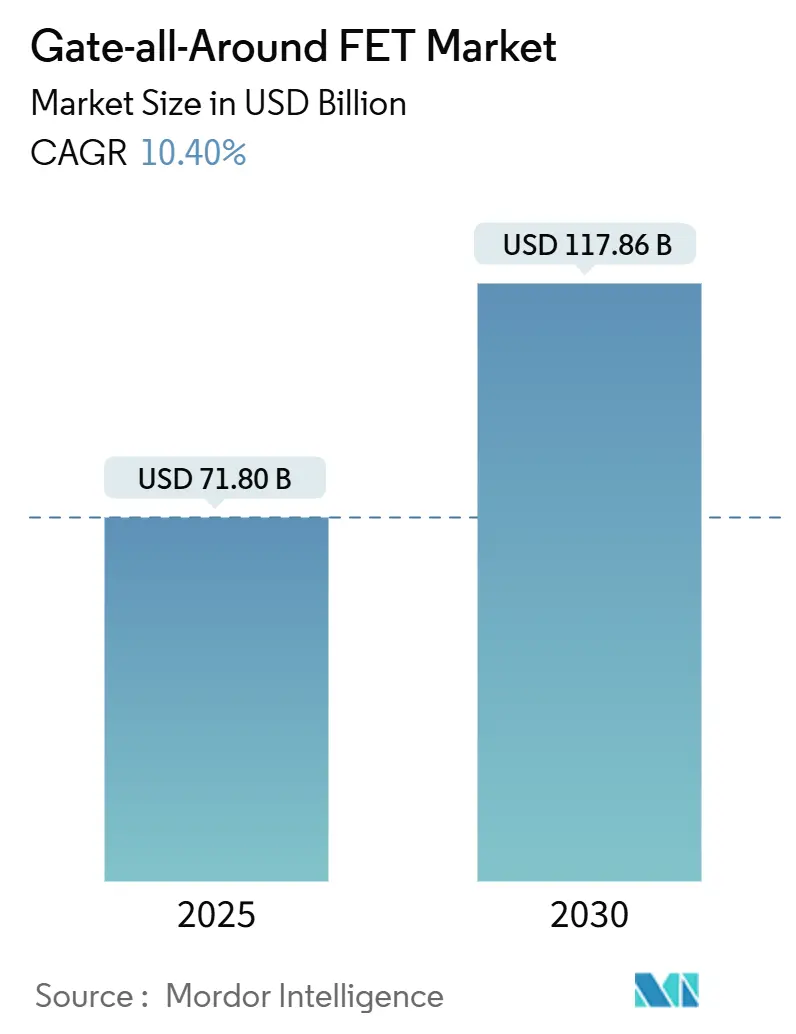

Gate-all-Around FET(GAAFET)市場は、2025年には718億米ドルに達し、2030年には1,178.6億米ドルに成長すると予測されており、予測期間中の年平均成長率(CAGR)は10.40%です。この成長は、3nm以下のノードで限界に達しているFinFET設計からの転換、人工知能(AI)および5Gワークロードにおける消費電力削減の緊急性、そしてGAAFETアーキテクチャが原子レベルでより厳密な静電制御を可能にするという実証された能力によって推進されています。アジア太平洋地域が最大の市場であり、最も急速に成長している地域でもあります。市場の集中度は高いです。

主要な市場動向と洞察

推進要因:

* 3nm以下のFinFETのスケーリング限界: FinFETは5nm以下のチャネル幅で基本的な静電的限界に直面し、許容できないリーク電流とばらつきを引き起こします。GAAFET構造は、チャネルをゲートで完全に包み込むことで制御を回復し、3nmの閾値を超えてムーアの法則を維持します。主要なファウンドリは、この不可避な移行に対応するため、GAAFETプロセス開発に500億米ドル以上を投資しています。

* AIおよび5G需要の急増: AI推論エンジンと5G無線は、より低い電圧でより高速にスイッチングするトランジスタを必要とします。GAAFETの垂直ゲートカバレッジは、ドレイン誘起障壁低下を低減し、サブスレッショルドスロープを改善することで、速度を犠牲にすることなく0.7V以下での動作を可能にします。これにより、エッジAIデバイスや5Gマクロ基地局での高性能化が実現し、GPUベンダーも次世代コアにGAAFETノードを採用しています。

* ファウンドリの生産ロードマップ: TSMCは2025年にリスク生産を開始する2nm容量に400億米ドルを投じ、ナノシートGAAFETデバイスに依存しています。Samsungも同様のナノシートラインで論理ICやモバイルSoCをターゲットにしており、IntelもGAAFETを再編されたIDM戦略に組み込んでいます。これらの同期されたロードマップは、ファブレス企業に量産可能性への安心感を与え、早期の設計参画を促します。

* 裏面電力供給ネットワーク(BPDN)との互換性: GAAFETデバイスは、アクティブ回路の下に電力を供給するBPDNと自然に組み合わせることができ、相互接続層を信号ルーティングに解放し、IRドロップを低減します。実験データによると、BPDNとの組み合わせにより電力供給効率が30%向上し、チップ面積が8%削減されます。これは、電力整合性がクロック周波数に直接影響する高コア数CPUやGPUで特に重要です。

阻害要因:

* 量産歩留まりの課題: GAAFETの初期歩留まりは40%から60%の範囲であり、成熟したFinFETラインの85%以上と比較して低く、ウェーハコストを上昇させ、プレミアムチップへの商業的実現可能性を限定しています。ナノシートの幅や間隔のばらつきはデバイスの故障を引き起こし、コストに敏感なセグメントへの普及を妨げます。今後2年間で、反復的なプロセス改良と設備アップグレードにより、歩留まりは高容量の家電製品と互換性のある経済的な閾値まで向上すると予想されます。

* 高額な設備投資要件: GAAFET製造は、極端紫外線(EUV)リソグラフィ、原子層堆積(ALD)、選択的エピタキシー、高密度プラズマエッチングツールに依存しており、最新の300mmファブを整備するには約200億米ドルが必要です。この資本集約度は、既存のメガファブに有利であり、小規模なIDMの参入を阻害し、競争力のあるサプライヤー基盤を集中させる傾向があります。一部の政府は、補助金プログラムを通じて先端ノードへの投資を支援し、初期費用を相殺し、国内供給ラインを確保しています。

セグメント分析

* トランジスタアーキテクチャ別:

* ナノシート設計が2024年に46%の収益シェアを占め、先行者としての優位性と既存のFinFETプロセスフローとの整合性を示しています。GAAFET市場におけるナノシートの市場規模は、2030年までに542億米ドルに達し、10.1%のCAGRで成長すると予測されています。

* フォークシートトランジスタは、2030年までに11.34%のCAGRで最も急速に成長すると予測されており、ナノシートを超える密度向上を追求するチップ設計者からの関心を集めています。

* ウェーハサイズ別:

* 300mm基板が2024年に63.62%の収益を占め、予測期間中に11.78%のCAGRで成長し、他の直径を上回ると予測されています。これは、ダイあたりのコストが低く、均一性制御が厳しいためです。

* アプリケーション別:

* スマートフォンおよびモバイルデバイスが2024年に31.73%の収益を占め、3nmアプリケーションプロセッサにおけるGAAFETロジックの最初の商用展開を支えています。

* 車載エレクトロニクスは、2030年までに10.99%のCAGRで急速に成長すると予測されています。これは、先進運転支援システム(ADAS)などが高密度コンピューティングを必要とするためです。

* エンドユーザー産業別:

* ファウンドリが2024年の売上高の54.83%を占め、製造と技術実現における中心的な役割を反映しています。

* ファブレスIC設計者は、年間11.55%で成長しており、資本支出なしで2nmおよびフォークシートノードへの早期アクセスを得るためにファウンドリモデルを活用しています。

地域分析

* アジア太平洋地域は、2024年に56.73%のシェアを占め、2030年までに11.66%のCAGRで拡大すると予測されています。これは、台湾の支配的なファウンドリ拠点、韓国のプロセスブレークスルー、中国の多額の国家資金によって推進されています。

* 北米は、活気あるファブレスハブとCHIPSおよび科学法に基づく連邦政府の新たなインセンティブに支えられ、かなりの収益を上げています。Intelはアリゾナ州とオハイオ州に2nm GAAFETの量産を目的とした数十億ドルの投資を行っています。

* 欧州は、欧州チップス法を通じてパイロットラインとエコシステム構築に資金を提供することで、技術主権を追求しています。ドイツの自動車サプライチェーンは、機能安全プロトコルを満たすGAAFETチップへの長期的な現地アクセスを求めています。

* 中東およびアフリカは現在、家電製品やデータセンターの新興需要プールとして機能していますが、意味のある製造能力は不足しています。

競争環境

GAAFET市場の競争は、最先端のプロセスノードを制御し、数十億ドルの設備投資を展開できる少数のプレーヤーに集中しています。TSMC、Samsung、Intelが2nmロードマップの大部分を所有し、早期の顧客テープアウトコミットメントを確保するための三つ巴の競争を繰り広げています。各社は、歩留まり向上プログラム、材料革新、設備パートナーシップに積極的に投資しています。ASML、Applied Materials、Lam Researchなどの設備サプライヤーは、ファウンドリの生産タイムラインとツールロードマップを整合させる共同開発プロジェクトに参加しています。

知的財産の深さと整合されたEDAツールフローも競争の重要な側面です。CadenceとSynopsysは、GAAFETに最適化されたライブラリと設計ルールキットをリリースし、早期採用設計者との関係を強化しています。参入障壁は高く、各既存企業は設備、プロセスレシピ、IPの可用性においてエコシステムをロックインしています。

将来的には、標準的なナノシートの密度と性能の限界が近づくにつれて、競争はフォークシートや相補型積層ナノシートトポロジーへと移行する可能性があります。フロントエンドのデバイススケーリングとバックエンドの電力供給統合の両方を習得できるベンダーが、予測期間を通じて市場を上回るリターンを確保すると考えられます。

最近の業界動向

* 2025年3月: TSMCは、2026年に計画されている大量生産を支援するため、台湾で2nm GAAFETの生産能力を120億米ドル投資して拡大しました。

* 2025年2月: Samsungは、GAAFETのスケーリングと歩留まり最適化プログラムのために、韓国政府から85億米ドルのインセンティブを獲得しました。

* 2025年1月: Intelは、HPCプロセッサにおけるGAAFET統合を加速するため、欧州の設備企業から23億米ドルで先進パッケージング技術を買収しました。

* 2024年12月: Applied Materialsは、ナノシートチャネル形成に特化した選択的堆積システムを発表し、主要な歩留まり制限要因に対処しました。

本レポートは、次世代半導体技術であるGate-All-Around FET(GAAFET)の世界市場に関する詳細な分析を提供しています。GAAFETは、3nm以下のプロセスノードにおけるFinFET技術のスケーリング限界を克服し、高性能かつ低消費電力のチップを実現するための不可欠な技術として、半導体産業において極めて重要な注目を集めています。

GAAFETデバイス市場は、2030年までに1,178.6億米ドルに達すると予測されており、2024年から2030年にかけて年平均成長率(CAGR)10.40%で堅調に成長する見込みです。トランジスタアーキテクチャ別に見ると、既存のFinFETプロセスフローとの互換性が高く、迅速な歩留まり向上とコスト効率を実現するナノシートGAAFETが、2024年の売上高の46%を占め、現在市場を牽引しています。一方、より高いトランジスタ密度を可能にするフォークシートFETは、2030年までCAGR 11.34%で拡大すると予測されており、将来的な成長が期待されています。ナノワイヤGAAFETも重要なアーキテクチャの一つとして位置づけられています。

アプリケーション別では、スマートフォンやモバイルデバイス、高性能コンピューティング(HPC)およびデータセンターが主要な市場を形成しています。特に、先進運転支援システム(ADAS)や電気自動車(EV)に代表される車載エレクトロニクス分野では、電力効率の高い高性能チップへの需要が急速に高まっており、GAAFETの採用はCAGR 10.99%で成長すると予測されています。その他、Internet of Things(IoT)およびエッジデバイス、RFおよびアナログ分野でもGAAFETの活用が進んでいます。ウェハーサイズ別では300mmウェハーが主流であり、エンドユーザー産業としてはファウンドリ、Integrated Device Manufacturers(IDM)、ファブレスIC設計者、研究機関が挙げられます。

地域別では、アジア太平洋地域が先端GAA製造能力において主導的な地位を確立しており、台湾や韓国の強力なファウンドリ基盤により、2024年の収益の56.73%を占めています。北米、欧州、南米、中東およびアフリカも市場の重要な部分を構成しており、特に米国、中国、日本、ドイツなどが主要な市場国として挙げられます。

GAAFET市場の成長を推進する主な要因は多岐にわたります。具体的には、3nm以下のプロセスノードにおけるFinFETのスケーリング限界、AIや5Gといった高性能・低消費電力チップを要求するアプリケーション需要の急増が挙げられます。また、主要ファウンドリ各社がGAAFETの量産ロードマップを積極的に掲げていること、裏面電力供給(Backside Power Delivery)との互換性による性能向上、SiGeやSiBCNなどの高移動度チャネル材料の統合、さらには米国のCHIPS法や欧州のIPCEI-MEといった政府による先端ノードへのインセンティブも、市場拡大に寄与しています。

一方で、GAAFET市場の成長にはいくつかの阻害要因も存在します。最も大きな課題の一つは、GAAFET技術の量産歩留まりがまだ成熟しておらず、安定した生産体制の確立に時間を要することです。また、GAAFET製造には既存設備からの大幅な再ツール化や、高額な設備投資(CapEx)が必要となるため、参入障壁が高いという側面があります。GAAFET向けのEDA(Electronic Design Automation)ツールやIP(Intellectual Property)エコシステムがまだ発展途上であることも、設計・開発のボトルネックとなる可能性があります。さらに、積層ナノシート構造における自己発熱の問題は、チップの性能や信頼性に影響を与える可能性があり、技術的な解決が求められています。

競争環境のセクションでは、市場の集中度、主要企業の戦略的動向、市場シェア分析が詳述されています。Taiwan Semiconductor Manufacturing Company Limited (TSMC)、Samsung Electronics Co., Ltd.、Intel Corporationといった大手ファウンドリやIDMがGAAFET技術の開発と導入において主導的な役割を担っています。GlobalFoundries Inc.、Semiconductor Manufacturing International Corporation、Rapidus Corporationなども重要なプレイヤーです。Applied Materials, ASML Holding, Lam Research, Tokyo Electronといった半導体製造装置メーカーや、Cadence Design Systems, SynopsysといったEDAベンダーも、GAAFETエコシステムを支える上で不可欠な存在です。

本レポートは、GAAFET技術が半導体産業の未来を形作る上で不可欠な要素であり、技術的な課題や高コストといった障壁はあるものの、高性能・低消費電力チップへの需要の高まりと、主要企業の積極的な投資、政府の支援が、GAAFET市場のさらなる発展を後押しすると結論付けています。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

-

4.2 市場促進要因

- 4.2.1 3nm以下のFinFETのスケーリング限界

- 4.2.2 高性能・低消費電力チップに対するAI/5G需要の急増

- 4.2.3 GAAFET生産を約束するファウンドリのロードマップ

- 4.2.4 裏面電力供給互換性の利点

- 4.2.5 高移動度チャネル材料の統合 (SiGe, SiBCN)

- 4.2.6 先端ノード政府奨励金 (CHIPS, IPCEI-ME)

-

4.3 市場抑制要因

- 4.3.1 未熟な量産歩留まり

- 4.3.2 高額な再ツール費用と設備投資要件

- 4.3.3 ゲートオールアラウンドFET (GAAFET) の未熟なEDA/IPエコシステム

- 4.3.4 積層ナノシートにおける自己発熱

- 4.4 産業バリューチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

-

4.7 ポーターの5つの力分析

- 4.7.1 新規参入者の脅威

- 4.7.2 サプライヤーの交渉力

- 4.7.3 買い手の交渉力

- 4.7.4 代替品の脅威

- 4.7.5 競争上の対立

5. 市場規模と成長予測 (金額)

-

5.1 トランジスタアーキテクチャ別

- 5.1.1 ナノシートGAAFET

- 5.1.2 ナノワイヤーGAAFET

- 5.1.3 フォークシートFET

-

5.2 ウェーハサイズ別

- 5.2.1 300 mm

- 5.2.2 200 mm

- 5.2.3 150 mm未満

-

5.3 アプリケーション別

- 5.3.1 スマートフォンおよびモバイルデバイス

- 5.3.2 ハイパフォーマンスコンピューティングおよびデータセンター

- 5.3.3 車載エレクトロニクス (ADAS、EV)

- 5.3.4 モノのインターネットおよびエッジデバイス

- 5.3.5 RFおよびアナログ

- 5.3.6 その他のアプリケーション

-

5.4 エンドユーザー産業別

- 5.4.1 ファウンドリ

- 5.4.2 垂直統合型デバイスメーカー (IDM)

- 5.4.3 ファブレスIC設計者

- 5.4.4 研究機関および学術機関

-

5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 その他の南米諸国

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 フランス

- 5.5.3.3 イギリス

- 5.5.3.4 その他のヨーロッパ諸国

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 台湾

- 5.5.4.3 韓国

- 5.5.4.4 日本

- 5.5.4.5 インド

- 5.5.4.6 その他のアジア太平洋諸国

- 5.5.5 中東およびアフリカ

- 5.5.5.1 中東

- 5.5.5.2 アフリカ

6. 競合情勢

- 6.1 市場集中度

- 6.2 戦略的動き

- 6.3 市場シェア分析

-

6.4 企業プロファイル(グローバルレベルの概要、市場レベルの概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 台湾積体電路製造株式会社

- 6.4.2 サムスン電子株式会社

- 6.4.3 インテル株式会社

- 6.4.4 グローバルファウンドリーズ株式会社

- 6.4.5 中芯国際集成電路製造有限公司

- 6.4.6 力晶積成電子製造株式会社

- 6.4.7 華虹半導体有限公司

- 6.4.8 聯華電子株式会社

- 6.4.9 ラピダス株式会社

- 6.4.10 STマイクロエレクトロニクスN.V.

- 6.4.11 ネクスペリアB.V.

- 6.4.12 インフィニオンテクノロジーズAG

- 6.4.13 SKハイニックス株式会社

- 6.4.14 アプライド マテリアルズ株式会社

- 6.4.15 ASMLホールディングN.V.

- 6.4.16 ラムリサーチ株式会社

- 6.4.17 東京エレクトロン株式会社

- 6.4.18 KOKUSAI ELECTRIC株式会社

- 6.4.19 ケイデンス・デザイン・システムズ株式会社

- 6.4.20 シノプシス株式会社

- 6.4.21 シルバコ株式会社

- 6.4.22 imec(大学間マイクロエレクトロニクスセンター)

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

ゲートオールアラウンドFET(Gate-All-Around FET、GAA-FET)は、半導体デバイスの微細化と性能向上を追求する上で極めて重要な次世代トランジスタ構造です。従来のプレーナ型FETやFinFETの限界を克服し、ムーアの法則の継続を可能にする技術として注目されています。

定義

ゲートオールアラウンドFETは、チャネル(電流が流れる領域)をゲート電極が四方八方から完全に囲む構造を持つ電界効果トランジスタです。これにより、ゲートがチャネルに対する究極の静電制御を実現し、短チャネル効果(トランジスタが微細化された際に発生する望ましくない現象)を極限まで抑制します。プレーナ型FETではゲートがチャネルの上部のみを制御し、FinFETではゲートがチャネルの三面を制御していましたが、GAA-FETはチャネル全体を包み込むことで、リーク電流の低減、オン/オフ比の向上、駆動電流の強化、そしてさらなる微細化を可能にします。この構造は、特に3nm以降のプロセスノードにおいて、高性能かつ低消費電力の半導体デバイスを実現するために不可欠とされています。

種類

GAA-FETには、主にチャネルの形状によっていくつかの種類があります。

1. ナノワイヤ型GAA-FET: チャネルが円筒状の細いワイヤ(ナノワイヤ)で構成され、ゲートがそのワイヤを同心円状に囲む構造です。非常に優れた静電制御を提供しますが、駆動電流を確保するためには複数のナノワイヤを並列に配置する必要があります。

2. ナノシート型GAA-FET(MBCFET/RibbonFET): チャネルが薄いシート状の構造(ナノシート)で構成され、ゲートがそのシートを四方から囲む構造です。ナノワイヤ型と比較して、シートの幅を調整することで駆動電流を容易にスケーリングできる利点があります。このため、現在の最先端プロセスではナノシート型が主流となっており、Samsungは「MBCFET(Multi-Bridge-Channel FET)」、Intelは「RibbonFET」と呼称しています。

これらのチャネル構造は、水平方向に配置されるのが一般的ですが、将来的には垂直方向に積層することでさらなる高密度化を目指す「垂直GAA-FET」の研究も進められています。

用途

GAA-FETは、主に最先端のロジック半導体デバイスに適用されます。

* 高性能マイクロプロセッサ(CPU): サーバー、データセンター、パーソナルコンピュータ向けの高性能CPUにおいて、処理能力の向上と消費電力の削減に貢献します。

* グラフィックスプロセッサ(GPU): AI/機械学習、科学技術計算、ゲーミングなど、膨大な並列処理能力を要求されるGPUの性能向上に不可欠です。

* モバイルプロセッサ(SoC): スマートフォンやタブレットなどのモバイルデバイスにおいて、バッテリー寿命を延ばしつつ、より高度な機能(AI処理、高解像度グラフィックス)を実現します。

* AIアクセラレータ: エッジAIデバイスからクラウドAIインフラまで、AI処理に特化した半導体の効率と性能を大幅に向上させます。

GAA-FETの導入により、これらのデバイスはより高い集積度、高速な動作、そして大幅に低い消費電力を実現できるようになります。

関連技術

GAA-FETの実現には、様々な高度な半導体製造技術が不可欠です。

* EUVリソグラフィ(極端紫外線リソグラフィ): 微細なチャネルやゲートパターンを形成するために、従来のDUV(深紫外線)リソグラフィよりも短い波長の光を用いるEUVリソグラフィが必須です。

* 原子層堆積(ALD): ゲート絶縁膜や金属ゲート電極を、チャネルの複雑な三次元形状に沿って原子レベルで精密に堆積させるために用いられます。これにより、均一で高品質な薄膜形成が可能になります。

* 選択的エッチング: ナノシートやナノワイヤ構造を形成する際に、犠牲層を精密に除去し、目的のチャネル材料のみを残すために高度な選択的エッチング技術が用いられます。

* 高誘電率(High-k)ゲート絶縁膜と金属ゲート: リーク電流を抑制し、ゲート制御能力を高めるために、従来のSiO2に代わるHigh-k材料と、それに適した金属ゲート材料が使用されます。

* 応力(Strain)エンジニアリング: チャネル材料に意図的に応力を加えることで、電子や正孔の移動度を高め、トランジスタの駆動電流を向上させる技術です。

* 3D積層技術: GAA-FET自体が3D構造ですが、さらに複数のチップやメモリを垂直方向に積層する3D積層技術と組み合わせることで、システム全体の性能と集積度をさらに高めることが期待されます。

市場背景

半導体市場において、GAA-FETはムーアの法則の継続と、それに伴う性能向上・コスト削減の鍵を握る技術として位置づけられています。FinFETが7nm/5nm世代で限界に近づく中、3nm以降のプロセスノードではGAA-FETの導入が不可避とされています。

主要な半導体ファウンドリであるTSMC、Samsung、Intelは、それぞれ独自のGAA-FET技術を開発し、量産体制の確立を競っています。Samsungは2022年に3nmプロセスでMBCFETの量産を開始したと発表し、TSMCも3nmプロセスでGAA-FETの導入を進めています。Intelも20A(2nm相当)プロセスでRibbonFETを導入する計画です。

この技術競争は、高性能コンピューティング、AI、5G/6G通信、自動運転など、次世代技術の発展を支える基盤となります。GAA-FETの導入は、開発コストと製造コストの増大を伴いますが、市場の要求に応えるためには不可欠な投資と見なされています。電力効率の向上は、データセンターの消費電力問題やモバイルデバイスのバッテリー寿命延長にも直結するため、環境負荷低減の観点からも重要性が増しています。

将来展望

GAA-FETは、今後数世代にわたる半導体微細化の主役として、さらなる進化を遂げると予想されます。

* さらなる微細化: 2nm、1.4nm、さらには1nm以下のプロセスノードに向けて、GAA-FET構造の最適化と、より微細なチャネル形成技術が追求されます。

* 新材料の導入: シリコンに代わる、あるいはシリコンと組み合わせる形で、2次元材料(例: MoS2、WSe2)などの超薄型チャネル材料の研究が進められています。これらの材料は、究極の静電制御と高い移動度を両立させ、さらなる性能向上と低消費電力化に貢献する可能性があります。

* 垂直GAA-FETの実現: 現在主流の水平GAA-FETに加え、チャネルを垂直方向に積層する垂直GAA-FETが、将来的な高密度化とフットプリント削減の切り札となる可能性があります。これにより、チップ面積あたりのトランジスタ数を飛躍的に増やすことが期待されます。

* 異種材料・デバイスとの統合: GAA-FETは、量子コンピューティングやニューロモルフィックコンピューティングといった次世代コンピューティング技術とのインターフェースとしても機能する可能性があります。また、メモリやセンサーなど、異なる機能を持つデバイスとの3D統合も進むでしょう。

しかし、GAA-FETの進化には、製造プロセスの複雑化、コストの増大、熱管理の課題、そして量子効果による新たな物理的限界など、多くの課題が伴います。これらの課題を克服し、持続的な技術革新を続けることが、半導体産業の未来を切り拓く鍵となります。