高度パッケージング市場 規模・シェア分析 – 成長トレンドと予測 (2026-2031年)

アドバンストパッケージング市場は、パッケージングプラットフォーム(フリップチップ、エンベデッドダイ、ファンインWLPなど)、エンドユーザー産業(家電、自動車・EV、データセンター・HPCなど)、デバイスアーキテクチャ(2D IC、2.5Dインターポーザー、3D IC)、相互接続技術(はんだバンプ、銅ピラー、ハイブリッドボンド)、および地域(北米、南米、欧州、アジア太平洋、中東・アフリカ)によってセグメント化されています。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

先進パッケージング市場の概要

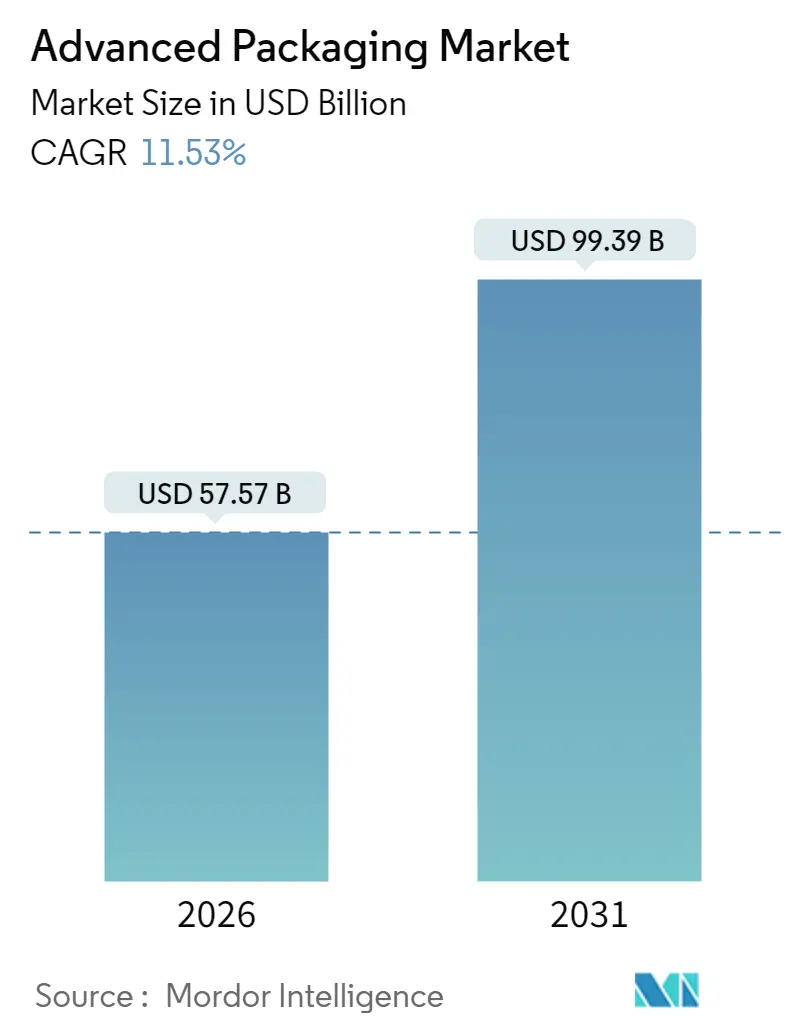

先進パッケージング市場は、2025年の516.2億米ドルから2026年には575.7億米ドルに成長し、2031年までに993.9億米ドルに達すると予測されており、2026年から2031年までのCAGR(年平均成長率)は11.53%と見込まれています。この成長は、従来のパッケージの熱的および相互接続の限界を超えるAIプロセッサにおいて、ヘテロジニアス統合が不可欠になったことによる需要の増加が主な要因です。これに対応し、IDM(垂直統合型デバイスメーカー)やOSAT(半導体後工程受託サービス)プロバイダーは設備投資を加速させ、各国政府も組立能力の現地化を促進するための大規模なインセンティブを投入しています。

市場は、フリップチップ、埋め込みダイ、ファンインWLPなどのパッケージングプラットフォーム、家電、自動車・EV、データセンター・HPCなどのエンドユーザー産業、2D IC、2.5Dインターポーザー、3D ICなどのデバイスアーキテクチャ、はんだバンプ、銅ピラー、ハイブリッドボンドなどの相互接続技術、そして北米、南米、欧州、アジア太平洋、中東・アフリカといった地域によってセグメント化されています。

主要な市場動向と洞察

成長要因:

1. AIおよびHPC向けヘテロジニアス統合の需要増加: AIワークロードは、従来のパッケージでは達成できない高い演算密度とメモリ帯域幅を要求します。TSMCのCoWoSプラットフォームやSamsungのSAINT技術は、チップレットと高帯域幅メモリを統合し、AIアクセラレータベンダーの間で急速に採用されています。これにより、パッケージコストが半導体BOM(部品表)全体の15~20%に上昇し、先進パッケージング能力がAIシステムの市場投入時期を決定する上で極めて重要になっています。

2. 民生機器の小型化によるWLP(ウェハーレベルパッケージング)採用の促進: スマートフォン、ウェアラブル、ヒアラブルなどの民生機器は、より薄いプロファイルと高い機能密度を常に求めています。FOWLP(ファンアウトウェハーレベルパッケージング)は、複数のダイを0.5mm以下の超薄型パッケージに組み込むことを可能にし、熱性能を損なうことなくモバイルプロセッサをサポートします。医療用埋め込み型電子機器においても、WLPはデバイスサイズの劇的な削減に貢献しています。

3. 政府による半導体補助金によるインフラ開発の加速: 米国のCHIPSおよび科学法(527億米ドル、うち16億米ドルが先進パッケージング向け)や欧州のChips Act(約486億米ドル)などの法案は、国内能力の強化を目的としています。これにより、Amkorがアリゾナ州に20億米ドルの施設を建設したり、onsemiがチェコ共和国に20億米ドルのSiCパッケージングサイトを設立したりするなど、大規模な投資が誘発され、新たな生産ラインの立地選定に影響を与えています。

4. EVパワーエレクトロニクス信頼性要件の変化: 800V車載アーキテクチャへの移行は、熱、電圧、機械的堅牢性における抜本的な改善を必要としています。EVインバーター向けパッケージは、20年間にわたる-40℃から+150℃の熱サイクルに耐える必要があり、先進材料、ボイドフリー焼結、両面冷却トポロジーが不可欠です。これにより、自動車用SiCモジュールのパッケージ価値は従来のシリコンデバイスの3~4倍に上昇し、パッケージングが差別化の要素となっています。

5. ハイパースケールデータセンターにおけるCo-packaged opticsの需要: データセンターにおけるCo-packaged opticsの採用も市場を牽引しています。

6. 新興のガラスコア基板によるパネルレベルパッケージングの実現: ガラスコア基板の研究開発も進展しており、パネルレベル処理のパイロットプロジェクトが市場に貢献しています。

抑制要因:

1. 先進パッケージングラインの高い設備投資: 2.5Dおよび3Dプロセスのツールは、チャンバーあたり1,000万~1,500万米ドルと高額であり、従来のラインの300万米ドルを大幅に上回ります。これにより、中小規模のOSATは投資回収に苦慮し、ニッチな専門化や合併を余儀なくされています。

2. 業界統合による受託製造マージンの圧迫: ファウンドリがAIサプライチェーンのエンドツーエンド制御を確保するためにパッケージングを内製化する動きが強まり、従来のOSATのマージンを圧迫しています。

3. BT樹脂基板の供給ボトルネック: 2.5Dインターポーザーに使用される高密度ビルドアップ基板は、限られた日本および台湾企業から供給されるBT樹脂に依存しています。最先端基板のリードタイムは24週間に倍増し、パッケージの再設計やBOMコストの増加を招いています。

4. 高度な組立技術者の不足: 世界的に高度な組立技術者の不足が深刻であり、特に北米と欧州で顕著です。

セグメント分析

* パッケージングプラットフォーム別: フリップチップ技術が2025年に48.30%の収益を占め、引き続き主導的地位を維持しています。しかし、2.5D/3Dソリューションは、AIアクセラレータの需要に牽引され、2031年までに13.05%のCAGRで最も速い成長が予測されており、市場規模は389億米ドルに達すると見込まれています。

* エンドユーザー産業別: 民生機器が2025年の需要の39.20%を占めましたが、成長は一桁台に落ち着いています。対照的に、自動車およびEV分野は12.32%のCAGRで拡大し、2031年までに先進パッケージング市場の18.6%を占め、市場規模は185億米ドルを超えると予測されています。データセンターやヘルスケア分野も高い成長が期待されています。

* デバイスアーキテクチャ別: 2D ICが2025年に55.10%のシェアを占めましたが、3D ICは14.86%のCAGRで成長し、2031年までに市場シェアは29.2%に達すると予測されています。TSV(Through-Silicon-Via)やハイブリッドボンドスタックがAIやネットワーキングデバイスで主流になるにつれて、垂直統合がムーアの法則のような進歩を維持する中心的な手段となっています。

* 相互接続技術別: はんだバンプが2025年に61.10%の収益を占め、レガシーノードにおけるコスト競争力を反映しています。銅ピラーも性能重視のフリップチップデバイスでシェアを伸ばしていますが、最も速い成長はハイブリッドボンドで、17.18%のCAGRが予測されており、2031年までに市場規模は207億米ドルに達すると見込まれています。ハイブリッドボンドは、10µm以下の直接金属間接触を可能にし、HBM4生産などで信号遅延を40%削減し、帯域幅を倍増させています。

地域分析

* アジア太平洋: 2025年の収益の74.10%を占め、台湾、韓国、中国本土にフロントエンドファブと基板サプライヤーが集中しているため、引き続き市場をリードしています。TSMCの米国への大規模投資は、台湾拠点の代替ではなく、多様化戦略を反映しており、アジアが中期的には主導的地位を維持すると考えられます。

* 北米: CHIPS Actのインセンティブにより、12.38%のCAGRで最も速い成長地域となっています。Amkorのアリゾナ州の20億米ドルの施設は、米国システムインテグレーターに近い初の大型受託オプションを提供し、Intel、Apple、NVIDIAなどが地政学的リスクを軽減するためにこの能力の一部を予約しています。

* 欧州: onsemiのチェコ共和国施設が自動車用SiCデバイスに特化するなど、量よりも専門化を追求しています。

* シンガポール: MicronのHBM工場やKLAのプロセス制御拡張により、AIメモリと計測をサポートする垂直統合型エコシステムを構築し、ハブとしての役割を強化しています。

* インド: 50%の設備投資費用分担スキームを導入し、先進パッケージングのパイロットプロジェクトを誘致しています。

これらの動向は、システムOEMにとって地理的リスクを多様化し、先進パッケージング市場のバランスを再構築しています。しかし、既存のインフラ、サプライチェーンクラスター、規模の経済により、アジア太平洋地域は2031年にも60%以上のシェアを維持すると予測されています。

競争環境

市場は、ファウンドリがAIの価値プールを獲得するためにパッケージングを垂直統合する動きにより、中程度の競争から激しい競争へと移行しています。TSMC、Samsung、Intelは、自社製3Dパッケージングをサブ2nmウェハー技術と同等の戦略的重要性を持つものとして推進しており、フロントエンドとバックエンドの境界を曖昧にしています。OSATは、JCETが車載グレードモジュールに注力し、ASEがスマートフォンアプリケーションプロセッサ向けのパネルレベルファンアウトラインに投資するなど、専門化によって対応しています。

2.5Dラインの高い設備投資は、特にコモディティ化されたフリップチップ収益に依存する二流プロバイダーにとって、投下資本利益率を圧迫し、マージン圧力が強まっています。政府の補助金は設備投資の一部を相殺しますが、補助金へのアクセスは大手企業に有利に働き、統合を加速させています。

技術的差別化が主要な競争軸となっています。Samsungはハイブリッドボンドを活用してHBM4契約を獲得し、Amkorはアリゾナ州の施設を通じて米国顧客への地理的近接性を強調しています。JCETは車載信頼性基準への早期の注力により、2023年に88%の収益増を達成し、将来のEVモジュール標準に影響を与える立場を確立しました。

主要企業:

Amkor Technology, Inc.、Taiwan Semiconductor Manufacturing Company Limited、Advanced Semiconductor Engineering Inc.、Intel Corporation、JCET Group Co. Ltd.などが主要なプレーヤーとして挙げられます。

最近の業界動向:

* 2025年3月: TSMCが3つのファブと2つの先進パッケージング施設を含む1,650億米ドルの米国拡張計画を発表。

* 2025年1月: Micronがシンガポールに70億米ドルの高帯域幅メモリパッケージング工場を着工。

* 2024年10月: KLAがシンガポールでのプロセス制御ソリューション向け2億米ドルの拡張計画のフェーズ1を完了。

* 2024年7月: Amkorがアリゾナ州の20億米ドルの施設に対し、CHIPS Actから4億700万米ドルの支援を獲得。

「先進パッケージング」は、従来の集積回路パッケージングに先立ち、複数のコンポーネント(電気、機械、半導体など)を集約・相互接続し、単一の電子デバイスとしてパッケージ化する技術を指します。この技術は、半導体製造施設におけるプロセスと手法を用いています。本レポートは、先進パッケージング市場の全体像、成長予測、主要な推進要因と阻害要因、および競争環境について詳細に分析しています。

市場は2026年から2031年にかけて年平均成長率(CAGR)11.53%で成長し、2031年には993.9億米ドルに達すると予測されています。

この成長を牽引する主な要因としては、AIおよびHPC(高性能コンピューティング)向けヘテロジニアス統合の需要増加、民生機器の小型化によるWLP(ウェハーレベルパッケージング)採用の促進が挙げられます。また、CHIPS法やEUチップス法などの政府による半導体補助金、EV(電気自動車)のパワーエレクトロニクスにおける高い信頼性要件、新興のガラスコア基板によるパネルレベルパッケージングの実現、ハイパースケールデータセンターにおけるコパッケージドオプティクス(Co-packaged optics)の需要も市場拡大に寄与しています。

一方で、市場の成長を抑制する要因も存在します。先進パッケージングラインの高い設備投資、業界統合によるアウトソースマージンの圧迫、BT樹脂基板の供給ボトルネック、および高度な組み立て技術を持つ人材の不足が挙げられます。

パッケージングプラットフォーム別では、2.5D/3D技術がCAGR 13.05%と最も速い成長を遂げると見込まれています。地域別では、北米がCHIPS法によるインセンティブとAmkorの20億ドル規模のアリゾナ工場建設などの大規模な民間投資により、2031年までにCAGR 12.38%で最も急速に成長する市場となるでしょう。

エンドユーザー産業別では、EVパワーエレクトロニクスやドメインコントローラーにおける高信頼性パッケージの需要により、自動車およびEVアプリケーションがCAGR 12.32%で成長すると予測されています。

相互接続技術では、ハイブリッドボンディングが10µm以下のピッチで直接金属間接続を形成し、従来の半田バンプよりも高い帯域幅と優れた熱性能を実現するため、CAGR 17.18%で最も急速に成長するセグメントとなっています。

本レポートでは、市場を以下の主要なセグメントに分類し、詳細な分析を提供しています。

* パッケージングプラットフォーム別: フリップチップ、埋め込みダイ、ファンインWLP、ファンアウトWLP、2.5D/3D。

* エンドユーザー産業別: 民生用電子機器、自動車およびEV、データセンターおよびHPC、産業用およびIoT、ヘルスケア/メドテック。

* デバイスアーキテクチャ別: 2D IC、2.5Dインターポーザー、3D IC(TSV/ハイブリッドボンド)。

* 相互接続技術別: 半田バンプ、銅ピラー、ハイブリッドボンド。

* 地域別: 北米、南米、ヨーロッパ、アジア太平洋、中東およびアフリカ。

競争環境の分析では、市場集中度、戦略的動向、市場シェア分析が含まれており、Amkor Technology, Inc.、Taiwan Semiconductor Manufacturing Company Limited (TSMC)、Advanced Semiconductor Engineering, Inc. (ASE)、Samsung Electronics Co., Ltd.、Intel Corporationなど、主要なグローバル企業25社以上のプロファイルが提供されています。

本レポートは、市場の機会と将来の展望についても言及しており、未開拓の分野や満たされていないニーズの評価を通じて、今後の成長戦略策定に役立つ情報を提供しています。

1. はじめに

- 1.1 調査の前提と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

- 4.2 マクロ経済要因の影響

- 4.3 市場の推進要因

- 4.3.1 AIおよびHPC向けヘテロジニアス統合の需要増加

- 4.3.2 消費者デバイスの小型化がWLPの採用を促進

- 4.3.3 政府による半導体補助金(例:CHIPS法、EU半導体法)

- 4.3.4 EVパワーエレクトロニクスの信頼性要件(先進パワーパッケージ)

- 4.3.5 パネルレベルパッケージングを可能にする新興のガラスコア基板

- 4.3.6 ハイパースケールデータセンターにおけるコパッケージドオプティクスの需要

- 4.4 市場の阻害要因

- 4.4.1 先進パッケージングラインの高い設備投資強度

- 4.4.2 業界統合による外部委託マージンの圧迫

- 4.4.3 BT樹脂基板の生産能力のボトルネック

- 4.4.4 先進アセンブリ人材の不足

- 4.5 バリューチェーン分析

- 4.6 規制環境

- 4.7 技術的展望

- 4.8 ポーターの5つの力分析

- 4.8.1 新規参入の脅威

- 4.8.2 買い手の交渉力

- 4.8.3 供給者の交渉力

- 4.8.4 代替品の脅威

- 4.8.5 競争の激しさ

- 4.9 投資分析

5. 市場規模と成長予測(金額)

- 5.1 パッケージングプラットフォーム別

- 5.1.1 フリップチップ

- 5.1.2 エンベデッドダイ

- 5.1.3 ファンインWLP

- 5.1.4 ファンアウトWLP

- 5.1.5 2.5D / 3D

- 5.2 エンドユーザー産業別

- 5.2.1 家庭用電化製品

- 5.2.2 自動車およびEV

- 5.2.3 データセンターおよびHPC

- 5.2.4 産業およびIoT

- 5.2.5 ヘルスケア / メドテック

- 5.3 デバイスアーキテクチャ別

- 5.3.1 2D IC

- 5.3.2 2.5Dインターポーザー

- 5.3.3 3D IC (TSV / ハイブリッドボンド)

- 5.4 相互接続技術別

- 5.4.1 ソルダーバンプ

- 5.4.2 銅ピラー

- 5.4.3 ハイブリッドボンド

- 5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米諸国

- 5.5.3 欧州

- 5.5.3.1 ドイツ

- 5.5.3.2 フランス

- 5.5.3.3 イギリス

- 5.5.3.4 イタリア

- 5.5.3.5 オランダ

- 5.5.3.6 ロシア

- 5.5.3.7 その他の欧州諸国

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 台湾

- 5.5.4.3 韓国

- 5.5.4.4 日本

- 5.5.4.5 シンガポール

- 5.5.4.6 マレーシア

- 5.5.4.7 インド

- 5.5.4.8 その他のアジア太平洋諸国

- 5.5.5 中東およびアフリカ

- 5.5.5.1 中東

- 5.5.5.1.1 イスラエル

- 5.5.5.1.2 アラブ首長国連邦

- 5.5.5.1.3 サウジアラビア

- 5.5.5.1.4 トルコ

- 5.5.5.1.5 その他の中東諸国

- 5.5.5.2 アフリカ

- 5.5.5.2.1 南アフリカ

- 5.5.5.2.2 ナイジェリア

- 5.5.5.2.3 その他のアフリカ諸国

6. 競争環境

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

- 6.4 企業プロファイル(グローバル概要、市場概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 Amkor Technology, Inc.

- 6.4.2 Taiwan Semiconductor Manufacturing Company Limited

- 6.4.3 Advanced Semiconductor Engineering, Inc.

- 6.4.4 JCET Group Co., Ltd.

- 6.4.5 Samsung Electronics Co., Ltd.

- 6.4.6 Intel Corporation

- 6.4.7 Chipbond Technology Corporation

- 6.4.8 ChipMOS Technologies Inc.

- 6.4.9 Powertech Technology Inc.

- 6.4.10 TongFu Microelectronics Co., Ltd.

- 6.4.11 Nepes Corporation

- 6.4.12 STATS ChipPAC Pte. Ltd.

- 6.4.13 Siliconware Precision Industries Co., Ltd.

- 6.4.14 UTAC Holdings Ltd.

- 6.4.15 Walton Advanced Engineering, Inc.

- 6.4.16 Xintec Inc.

- 6.4.17 Tianshui Huatian Technology Co., Ltd.

- 6.4.18 King Yuan Electronics Co., Ltd.

- 6.4.19 Signetics Corporation

- 6.4.20 GlobalFoundries Inc.

- 6.4.21 Semiconductor Manufacturing International Corporation

- 6.4.22 SFA Semicon Co., Ltd.

- 6.4.23 Nantong Fujitsu Microelectronics Co., Ltd.

- 6.4.24 Hana Micron Inc.

- 6.4.25 Unisem (M) Berhad

7. 市場機会と将来の見通し

*** 本調査レポートに関するお問い合わせ ***

高度パッケージングとは、半導体チップの性能向上、小型化、多機能化、低消費電力化を実現するために、従来のパッケージング技術の限界を超えて進化させた、一連の高度な技術群を指します。単にチップを外部環境から保護し、電気的に接続するだけでなく、複数のチップを効率的に統合し、チップ間の高速信号伝送、安定した電力供給、効果的な熱放散などを最適化することを目的としています。ムーアの法則によるトランジスタの微細化が物理的・経済的な限界に近づく中で、「More than Moore(ムーアの法則を超えて)」戦略の中核を担い、システム全体の性能向上に不可欠な技術として注目されています。従来のパッケージングが主に2次元的な接続に留まっていたのに対し、高度パッケージングは3次元的な集積や異種デバイスの統合を特徴としています。

高度パッケージングには、様々な種類とアプローチが存在します。主要なものとしては、まず「2.5D/3Dパッケージング」が挙げられます。2.5Dパッケージングは、シリコンインターポーザや有機インターポーザといった中間基板を介して、複数のチップ(例えばCPU、GPU、HBMなどのメモリ)を水平に配置し、高密度な配線と高速通信を実現する技術です。代表的なものに、TSMC社のCoWoS(Chip-on-Wafer-on-Substrate)などがあります。一方、3Dパッケージングは、TSV(Through-Silicon Via:シリコン貫通電極)を用いてチップを垂直に積層し、配線長を極限まで短縮することで、超高速・大容量のデータ転送を可能にします。HBM(High Bandwidth Memory)がその代表例であり、プロセッサとメモリを密接に統合することで、AIや高性能コンピューティングの性能を飛躍的に向上させています。次に、「ファンアウト型パッケージング」があります。これは、従来のパッケージングがチップサイズよりもパッケージサイズが大きくなる傾向があったのに対し、チップのI/Oパッドを再配線層(RDL: Re-Distribution Layer)でチップ外に広げ、より多くのI/Oを確保しつつ、パッケージサイズをチップサイズに近づける、あるいは同等にする技術です。FO-WLP(Fan-Out Wafer Level Package)やFO-PLP(Fan-Out Panel Level Package)などがあり、高密度、薄型化、低コスト化に貢献します。さらに、「チップレット技術」も高度パッケージングの重要な要素です。これは、単一の巨大なSoC(System-on-a-Chip)を設計する代わりに、特定の機能を持つ小さなチップ(チップレット)を複数製造し、それらを2.5D/3Dパッケージングやインターポーザなどの高度パッケージング技術で統合するアプローチです。これにより、設計の柔軟性が向上し、歩留まりの改善、コスト削減、IP(Intellectual Property)の再利用促進が期待されます。UCIe(Universal Chiplet Interconnect Express)のような標準化も進んでいます。最後に、「異種集積(Heterogeneous Integration)」は、異なるプロセスで製造された、あるいは異なる機能を持つチップ(ロジック、メモリ、RF、センサー、パワーデバイスなど)を一つのパッケージ内に統合する技術であり、高度パッケージングはこれを実現するための基盤技術として不可欠です。

高度パッケージングは、多岐にわたる分野で活用されています。最も顕著なのは、AIアクセラレータ、データセンター、スーパーコンピュータなどの「高性能コンピューティング(HPC)」分野です。ここでは、HBMとプロセッサの統合に2.5D/3Dパッケージングが不可欠であり、膨大なデータ処理能力と高速演算性能を実現しています。また、スマートフォンやウェアラブルデバイスといった「モバイルデバイス」では、小型化、薄型化、多機能化、低消費電力化が求められ、SiP(System-in-Package)やファンアウト型パッケージングが活用されています。さらに、「自動車」分野では、ADAS(先進運転支援システム)や自動運転向けの高信頼性、高性能、低遅延なプロセッサが必要とされ、異種集積や高放熱パッケージングが重要性を増しています。「IoTデバイス」においても、センサー、通信モジュール、マイコンの統合による小型化、低コスト化、低消費電力化に貢献しています。その他、「ネットワーク機器」においても、高速データ処理と大容量通信を実現するための高密度集積に不可欠な技術となっています。

高度パッケージングを支える関連技術も多岐にわたります。3D積層の鍵となる「TSV(Through-Silicon Via)」は、シリコンウェハを貫通する電気的接続を可能にし、チップ間の配線長を大幅に短縮します。チップ間の微細な接続技術としては、「マイクロバンプ」や、より高密度な接続を可能にする「ハイブリッドボンディング」があります。ハイブリッドボンディングは、バンプを介さずにチップを直接接合する技術です。ファンアウト型パッケージングやインターポーザにおける「RDL(Re-Distribution Layer)」は、再配線層として機能し、I/Oパッドの配置を柔軟にします。2.5Dパッケージングでチップ間を接続する中間基板である「インターポーザ」には、シリコン、有機、ガラスなど様々な材料が用いられます。高密度集積による発熱増大に対応するためには、「熱管理技術」が不可欠であり、高熱伝導材料や革新的な冷却構造の開発が進められています。また、高度化・複雑化するパッケージの品質を保証するためには、「検査・テスト技術」の進化も重要です。さらに、低誘電率材料、高熱伝導材料、高信頼性接合材料など、「材料技術」の進歩も高度パッケージングの発展を支えています。

高度パッケージングが注目される市場背景には、いくつかの要因があります。まず、「ムーアの法則の限界」が挙げられます。トランジスタの微細化による性能向上のペースが鈍化し、製造コストも増大する中で、パッケージングによる性能向上がより重要視されるようになりました。次に、「AI/HPCの需要増大」です。大規模なデータ処理や高速演算が求められるAIや高性能コンピューティングの分野では、HBMなどの高帯域幅メモリとプロセッサの統合が必須であり、高度パッケージングがその実現を可能にしています。また、「5G/IoTの普及」も大きな要因です。多様なデバイスの接続、小型化、低消費電力化、高信頼性が求められる中で、高度パッケージングはこれらの要件を満たす上で不可欠です。さらに、「異種デバイス統合の必要性」が高まっています。異なる機能を持つチップを効率的に統合し、システム全体の最適化を図ることで、より高性能で省電力なデバイスが実現できます。チップレット技術の登場により、異なるベンダーのチップを組み合わせることが可能になり、「サプライチェーンの多様化」と柔軟性の向上にも貢献しています。

将来の展望として、高度パッケージングはさらなる進化を遂げると予想されます。まず、「さらなる高密度化・微細化」が進むでしょう。マイクロバンプのさらなる微細化や、ハイブリッドボンディングの普及により、チップ間の接続密度は飛躍的に向上します。TSVの低コスト化と高信頼性化も進み、3D積層の適用範囲が拡大するでしょう。次に、「異種集積の進化」が加速します。チップ間やパッケージ間の通信を高速化し、低消費電力化するために、光インターコネクトの導入が進む可能性があります。また、MEMS、センサー、パワーデバイス、RFデバイスなど、より多様な機能を持つチップの統合が進み、システム全体の機能が向上します。さらに、「新材料・新構造の探求」も活発化します。ガラスインターポーザ、フレキシブル基板、液体冷却技術など、革新的な材料や構造が導入され、パッケージングの性能と信頼性が向上するでしょう。高度パッケージングの複雑な設計・製造プロセスにおいては、「AIを活用した設計・製造」が導入され、最適化と効率化が図られると見込まれます。チップレット間のインターフェース(UCIeなど)やパッケージング技術の「標準化の推進」も進み、エコシステムの拡大を促進するでしょう。最終的に、高度パッケージングは、小型化、低消費電力化を通じて、電子機器の環境負荷低減にも貢献し、「サステナビリティ」への貢献も期待されています。これらの進化により、高度パッケージングは、次世代の半導体技術と電子機器の発展を牽引する中核技術であり続けるでしょう。