アナログ/ミックスドシグナルIP市場規模・シェア分析 ー 成長動向と予測 (2025-2030年)

アナログ/ミックスドシグナルIP市場レポートは、設計(ファーム/ソフトIP、ハードIP)、製品(A2DおよびD2Aコンバーター、電源管理モジュール、RFなど)、エンドユーザー産業(家庭用電化製品、電気通信など)、プロセスノード(7nm以下、8nm~16nm、20nm~45nm、65nm以上)、および地域別に分類されます。市場予測は金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

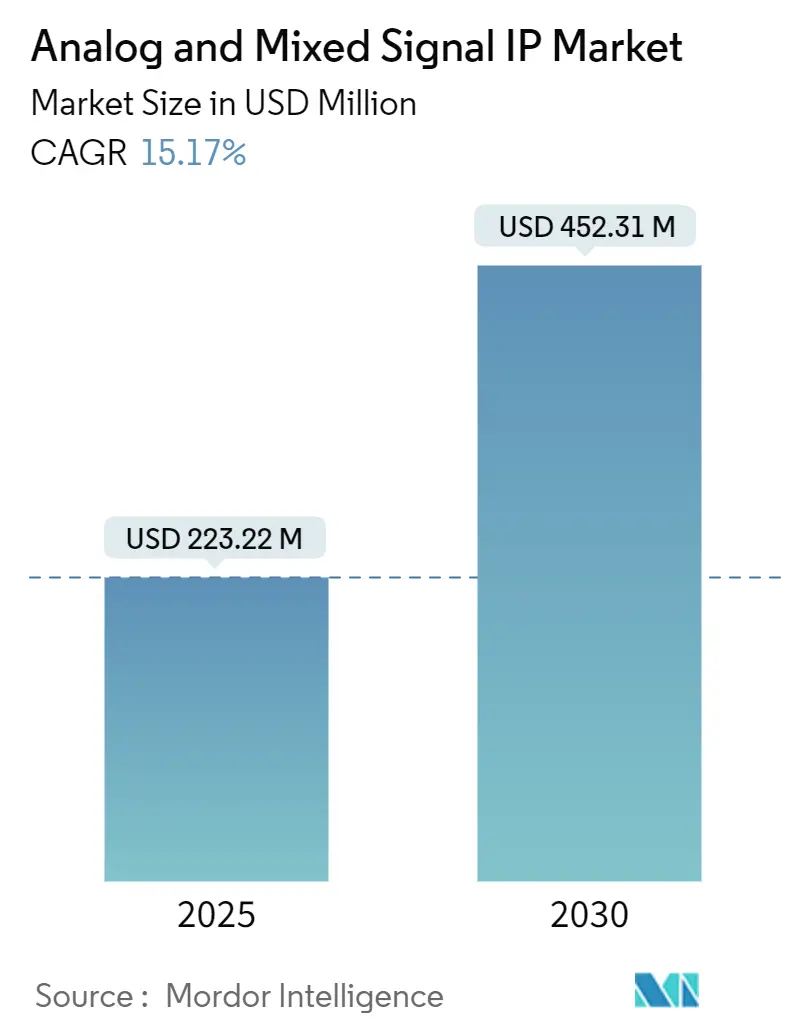

アナログおよびミックスドシグナルIP市場は、2025年から2030年にかけて堅調な成長が見込まれています。2025年には2億2,322万米ドル規模に達し、2030年には4億5,231万米ドルに拡大すると予測されており、この期間の年平均成長率(CAGR)は15.17%です。この成長は、データコンバーター、電源レギュレーター、RFトランシーバーなどが高度なデジタルノード上で共存するヘテロジニアス統合型システムオンチップ(SoC)への移行、自動車OEMによる100以上の制御ユニットをゾーン型ドメインコントローラーに統合する動き、そしてレガシーデバイスでは対応できない超低電力アナログフロントエンドを必要とするエッジAI推論プロセッサーの需要によって支えられています。

2024年10月に中国に課された電子設計自動化(EDA)ツールに関する輸出管理規則は、世界のサプライチェーンを分断し、中国のファブレス企業がプロジェクトの遅延を避けるために国内のIPブロックを調達する動きを促しています。アジア太平洋地域は、中国の国営ファブや日本の企業と台湾積体電路製造(TSMC)との合弁事業が先端ノードの生産能力を確保していることから、引き続き需要の中心地となっています。スマートフォンや5G基地局におけるミリ波RFフロントエンドのライセンス活動の急速な増加も、アナログおよびミックスドシグナルIP市場の成長軌道をさらに押し上げています。

主要なレポートのポイント

* 設計フォーマット別: ファームIPおよびソフトIPが2024年に市場シェアの54.59%を占めましたが、ハードIPは2030年までに17.11%のCAGRで成長すると予測されています。

* 製品タイプ別: 電源管理モジュールが2024年に36.71%の収益シェアを占め、RF IPは2030年までに16.59%のCAGRで拡大すると予測されています。

* エンドユーザー産業別: 消費者向け電子機器が2024年に30.15%の収益シェアを占め、自動車産業は2030年までに17.88%のCAGRで成長すると予測されています。これらの分析は、アナログおよびミックスドシグナルIP市場が今後も技術革新と多様なアプリケーションによって牽引され、持続的な成長を遂げる可能性を示しています。

本レポートは、アナログおよびミックスドシグナルIP市場に関する詳細な分析を提供しています。市場の定義、調査範囲、調査方法から始まり、市場の現状、将来予測、主要な推進要因と阻害要因、競争環境、そして市場機会と将来の展望について包括的に記述されています。

市場規模に関して、アナログおよびミックスドシグナルIP市場は2025年に2億2,322万米ドルに達すると予測されており、2030年には4億5,231万米ドルに成長すると見込まれています。地域別では、アジア太平洋地域が2024年に市場最大の41%のシェアを占め、2030年まで年平均成長率(CAGR)15.93%で成長すると予測されています。製品カテゴリー別では、RF IPが最も急速に成長しており、2025年から2030年にかけてCAGR 16.59%で拡大すると予測されています。ハードIPの採用は、チップレットベースの設計とUniversal Chiplet Interconnect Express (UCIe)によるプラグアンドプレイ統合の進展により加速しており、CAGR 17.11%での成長が見込まれています。エンドユーザー産業別では、自動車分野、特に電気自動車のバッテリー管理システムやゾーンコントローラーが、2030年までCAGR 15.78%で最も高い成長勢いを示しています。

市場の成長を牽引する主要な要因としては、以下の点が挙げられます。低消費電力コネクテッドデバイスへの需要の高まり、エッジAI推論ワークロードの急速な普及、スマートフォンにおける5G対応RFフロントエンドの拡大、自動車OEMによるゾーンアーキテクチャへの転換、チップレットベースのヘテロジニアス統合の採用、そしてセキュリティ重視のアナログIP(物理的複製不可能機能:PUF)への注力強化です。

一方で、市場の成長を阻害する要因も存在します。アナログおよびミックスドシグナル(AMS)コシミュレーションにおける検証のボトルネックは、初回シリコン成功率を低下させ、テープアウトスケジュールに最大12ヶ月の遅延をもたらす可能性があります。その他、10nm以下のプロセスノードにおけるアナログ設計人材の不足、マルチダイシステムにおけるライセンスの複雑さ、EDA/IPに対する中国への地政学的輸出規制などが挙げられます。

本レポートでは、市場を以下の主要なセグメントにわたって詳細に分析しています。設計別(ファーム/ソフトIP、ハードIP)、製品別(A2DおよびD2Aコンバーター、電源管理モジュール、RF、その他の製品)、エンドユーザー産業別(家庭用電化製品、電気通信、自動車、産業、その他のエンドユーザー産業)、プロセスノード別(7nm以下、8nm~16nm、20nm~45nm、65nm以上)、そして地域別(北米、南米、欧州、アジア太平洋、中東、アフリカといった主要地域(各国を含む))。これらの分析に加え、バリューチェーン分析、規制環境、技術的展望、マクロ経済要因の影響、ポーターのファイブフォース分析も含まれています。

競争環境については、市場集中度、戦略的動向、市場シェア分析が行われています。主要企業としては、Cadence Design Systems Inc.、Synopsys Inc.、ARM Ltd.、Renesas Electronics Corporation、Intel Corporation、Advanced Micro Devices Inc. (Xilinx)など、多数のグローバル企業がプロファイルされています。各企業の概要、主要セグメント、財務情報、戦略的情報、製品・サービス、最近の動向などが網羅されています。

市場機会と将来の展望に関するセクションでは、未開拓の領域や満たされていないニーズの評価が行われ、今後の成長可能性が示唆されています。

1. はじめに

- 1.1 調査の前提と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

- 4.2 市場の推進要因

- 4.2.1 低消費電力接続デバイスの需要増加

- 4.2.2 エッジAI推論ワークロードの急速な普及

- 4.2.3 スマートフォンにおける5G対応RFフロントエンドの拡大

- 4.2.4 自動車OEMのゾーンアーキテクチャへの転換

- 4.2.5 チップレットベースのヘテロジニアス統合の採用

- 4.2.6 セキュリティ重視のアナログIP(物理的に複製不可能な機能)への注力強化

- 4.3 市場の阻害要因

- 4.3.1 AMSコシミュレーションにおける検証のボトルネック

- 4.3.2 10nm以下のノードにおけるアナログ設計人材の不足

- 4.3.3 マルチダイシステムにおけるライセンスの複雑さ

- 4.3.4 EDA/IPの中国への地政学的輸出規制

- 4.4 バリューチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

- 4.7 マクロ経済要因が市場に与える影響

- 4.8 ポーターの5つの力分析

- 4.8.1 新規参入者の脅威

- 4.8.2 買い手の交渉力

- 4.8.3 供給者の交渉力

- 4.8.4 代替品の脅威

- 4.8.5 競争の激しさ

5. 市場規模と成長予測(金額)

- 5.1 設計別

- 5.1.1 ファーム/ソフトIP

- 5.1.2 ハードIP

- 5.2 製品別

- 5.2.1 A2DおよびD2Aコンバーター

- 5.2.2 電源管理モジュール

- 5.2.3 RF

- 5.2.4 その他の製品

- 5.3 エンドユーザー産業別

- 5.3.1 家庭用電化製品

- 5.3.2 電気通信

- 5.3.3 自動車

- 5.3.4 産業

- 5.3.5 その他のエンドユーザー産業

- 5.4 プロセスノード別

- 5.4.1 7 nm以下

- 5.4.2 8 nm – 16 nm

- 5.4.3 20 nm – 45 nm

- 5.4.4 65 nm以上

- 5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米諸国

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 ロシア

- 5.5.3.6 その他のヨーロッパ諸国

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 韓国

- 5.5.4.4 インド

- 5.5.4.5 その他のアジア太平洋諸国

- 5.5.5 中東

- 5.5.5.1 サウジアラビア

- 5.5.5.2 アラブ首長国連邦

- 5.5.5.3 トルコ

- 5.5.5.4 その他の中東諸国

- 5.5.6 アフリカ

- 5.5.6.1 南アフリカ

- 5.5.6.2 ナイジェリア

- 5.5.6.3 その他のアフリカ諸国

6. 競争環境

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

- 6.4 企業プロファイル(グローバルレベルの概要、市場レベルの概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランク/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 ケイデンス・デザイン・システムズ社

- 6.4.2 シノプシス社

- 6.4.3 アーム社

- 6.4.4 ベリシリコン・ホールディングス社

- 6.4.5 シリコン・クリエーションズLLC

- 6.4.6 ルネサスエレクトロニクス株式会社

- 6.4.7 アドバンスト・マイクロ・デバイセズ社(ザイリンクス)

- 6.4.8 インテル株式会社

- 6.4.9 アナログ・デバイセズ社

- 6.4.10 テキサス・インスツルメンツ社

- 6.4.11 ランバス社

- 6.4.12 ファラデー・テクノロジー・コーポレーション

- 6.4.13 グローバルファウンドリーズ社

- 6.4.14 シーバ社

- 6.4.15 MACOMテクノロジー・ソリューションズ・ホールディングス社

- 6.4.16 インフィニオン・テクノロジーズAG

- 6.4.17 マイクロチップ・テクノロジー社

- 6.4.18 マーベル・テクノロジー社

- 6.4.19 セミファイブ社

- 6.4.20 アルファウェーブIPグループplc

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

アナログ/ミックスドシグナルIP(Intellectual Property)は、半導体設計において再利用可能なアナログ回路およびアナログとデジタル回路を統合したブロックを指します。これは、現代の複雑なシステムオンチップ(SoC)開発において、設計期間の短縮、開発コストの削減、およびリスクの低減に不可欠な要素となっています。

定義

IPとは、半導体チップ設計における特定の機能を持つ回路ブロックの設計資産のことです。アナログIPは、連続的な信号を処理する回路、例えばアンプ、フィルタ、データコンバータ(ADC/DAC)、PLL(Phase-Locked Loop)などを指します。一方、ミックスドシグナルIPは、アナログ回路とデジタル回路の両方を統合し、相互に連携して機能するブロックを指します。例えば、高速シリアライザ/デシリアライザ(SerDes)や、メモリインターフェースの物理層(PHY)などがこれに該当します。これらのIPは、特定のプロセス技術(例:28nm、16nm、7nmなど)向けに最適化され、性能、消費電力、面積(PPA)のバランスが考慮されて設計・検証済みであり、SoC設計者はこれらを自社のチップに組み込むことで、ゼロから設計する手間を省くことができます。

種類

アナログ/ミックスドシグナルIPには多岐にわたる種類があります。

1. データコンバータIP: アナログ信号をデジタル信号に変換するADC(Analog-to-Digital Converter)や、デジタル信号をアナログ信号に変換するDAC(Digital-to-Analog Converter)が含まれます。SAR(Successive Approximation Register)型、デルタシグマ型、パイプライン型など、用途に応じて様々なアーキテクチャが存在します。

2. コネクティビティ/インターフェースIP: 高速通信を実現するためのSerDes(Serializer/Deserializer)IP(PCIe、USB、Ethernet、MIPIなどに対応)、DDRメモリインターフェースのPHY IP、汎用入出力(GPIO)などが含まれます。これらは、チップ間の高速データ転送や外部デバイスとの接続に不可欠です。

3. 電源管理IP: LDO(Low-Dropout Regulator)、DC-DCコンバータ、電圧リファレンス、バンドギャップリファレンスなど、チップ内の様々なブロックに安定した電源を供給するためのIPです。PMIC(Power Management Integrated Circuit)の一部として提供されることもあります。

4. クロッキングIP: PLL(Phase-Locked Loop)やDLL(Delay-Locked Loop)、オシレータなど、チップ内の各ブロックに正確なクロック信号を供給するためのIPです。システムのタイミング精度と安定性を保証します。

5. センサーインターフェースIP: 温度、圧力、光、MEMS(Micro-Electro-Mechanical Systems)センサーなど、様々なセンサーからのアナログ信号を処理するためのアナログフロントエンド(AFE)IPです。

6. RF IP: 無線通信(Wi-Fi、Bluetooth、5Gなど)に必要なトランシーバ、LNA(Low Noise Amplifier)、ミキサ、PA(Power Amplifier)などのIPです。

7. オーディオ/ビデオIP: オーディオコーデック、アンプ、フィルタなど、マルチメディアアプリケーションに特化したIPです。

用途

アナログ/ミックスドシグナルIPは、現代のあらゆる電子機器に幅広く利用されています。

* 民生機器: スマートフォン、タブレット、スマートTV、ウェアラブルデバイスなどでは、オーディオコーデック、ディスプレイドライバ、電源管理、無線通信(Wi-Fi、Bluetooth、5G)のためのIPが不可欠です。

* 車載機器: ADAS(先進運転支援システム)、インフォテインメントシステム、自動運転システムなどでは、高速SerDes、センサーインターフェース、堅牢な電源管理IPが求められます。特に、過酷な環境下での高い信頼性が重視されます。

* 産業機器: IoTデバイス、ファクトリーオートメーション、医療機器などでは、高精度ADC、低消費電力RF、堅牢な通信IPが利用されます。

* データセンター/ネットワーキング: 高速SerDesは、光通信や電気通信の相互接続に不可欠であり、DDR PHYは高帯域幅メモリインターフェースに利用されます。

* 通信インフラ: 5G基地局などでは、高性能RFトランシーバや高速データコンバータが重要な役割を果たします。

* AI/機械学習アクセラレータ: 高帯域幅メモリインターフェースや効率的な電源管理IPが性能向上に貢献します。

関連技術

アナログ/ミックスドシグナルIPの設計と利用には、様々な関連技術が深く関わっています。

* 先端プロセスノード: FinFETやGAAFETといった微細化されたプロセス技術は、デジタル回路の性能向上に寄与しますが、アナログ回路にとっては低電源電圧、ノイズの増加、デバイスばらつきの増大といった課題をもたらします。そのため、高度な設計技術やDFM(Design for Manufacturability)が不可欠です。

* EDAツール: SPICEシミュレータ、レイアウトツール、AMS(Analog/Mixed-Signal)検証ツール、ミックスドシグナル協調シミュレーションツールなど、専門的な電子設計自動化(EDA)ツールが設計・検証に用いられます。

* パッケージング技術: 2.5D/3D ICなどの先進パッケージング技術は、異なるIP(RF、光、デジタル、アナログなど)を統合し、システム全体の性能と小型化を実現します。

* テスト・測定技術: ATE(Automatic Test Equipment)を用いたミックスドシグナルテストや特性評価は、IPの品質と信頼性を保証するために重要です。

* 低消費電力設計: アナログ回路における消費電力削減技術は、バッテリー駆動デバイスやIoTデバイスにおいて特に重要です。

* セキュリティ: IPの不正利用防止や、IPを組み込んだシステムのセキュリティ確保も重要な課題です。

市場背景

アナログ/ミックスドシグナルIP市場は、SoCの複雑化と開発期間短縮の要求により、急速に拡大しています。

* SoCの複雑化: 現代のSoCは、より多くの機能と高い性能を統合する必要があり、アナログ/ミックスドシグナルIPの再利用は、この複雑性に対処するための鍵となります。

* タイムツーマーケットの圧力: 競争の激しい市場において、製品を迅速に投入するためには、IPの活用による設計期間の短縮が不可欠です。

* コスト削減: IPを再利用することで、設計・検証にかかる時間とコストを大幅に削減できます。

* 専門化の進展: 半導体企業は、自社のコアコンピタンスに集中し、アナログ/ミックスドシグナルIPのような専門性の高いブロックは外部のIPベンダーから調達する傾向が強まっています。

* 特定市場の成長: IoT、AI、車載、5G、クラウドコンピューティングといった成長市場が、高性能かつ低消費電力のアナログ/ミックスドシグナルIPの需要を牽引しています。

主なIPベンダーとしては、Synopsys、Cadence、Arm、Rambusなどが挙げられますが、特定の分野に特化した専門IPベンダーも多数存在します。

将来展望

アナログ/ミックスドシグナルIPの将来は、技術革新と市場の拡大によって、さらなる進化が期待されます。

* 継続的な需要の増加: IoT、AI、車載、5G、エッジコンピューティングといった分野の発展に伴い、高性能、低消費電力、高信頼性のアナログ/ミックスドシグナルIPへの需要は今後も増加し続けるでしょう。

* さらなる微細化と課題克服: 7nm以下の先端プロセスノードへの移行は続き、アナログ回路設計における新たな課題(ノイズ、ばらつき、低電源電圧など)を克服するための革新的な設計技術が求められます。

* ヘテロジニアス統合の加速: 異なるプロセスで製造されたIPや、異なる機能を持つIP(RF、光、デジタル、アナログ)を単一のパッケージやチップレットに統合するヘテロジニアス統合が主流となり、IP間のインターフェース技術がより重要になります。

* AI/機械学習の活用: アナログ回路設計の自動化、最適化、検証プロセスにおいて、AIや機械学習技術の導入が進み、設計効率と品質の向上が期待されます。

* セキュリティ機能の強化: IPレベルでのセキュリティ機能(耐タンパー性、暗号化など)の強化が、IoTデバイスや車載システムにおいて重要性を増します。

* 特定用途向けIPの進化: 量子コンピューティングインターフェースやバイオセンサーなど、ニッチな分野に特化した高機能IPの開発が進むでしょう。

* オープンソースハードウェア/IPの台頭: デジタルIPに比べて複雑なアナログIPではまだ限定的ですが、オープンソースの動きが将来的に影響を与える可能性も秘めています。

アナログ/ミックスドシグナルIPは、半導体産業のイノベーションを支える基盤技術として、今後もその重要性を増していくことでしょう。