電子設計自動化(EDA)ツール市場:市場規模、シェア、成長トレンド、予測(2026年~2031年)

電子設計自動化ツールレポートは、ツールタイプ(コンピュータ支援エンジニアリング、IC物理設計および検証など)、設計フロー段階(フロントエンド設計RTLなど)、展開モード(オンプレミス、クラウドベース)、エンドユーザー産業(通信インフラ、家電など)、および地域(北米など)によってセグメント化されています。市場予測は金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

電子設計自動化(EDA)ツール市場の概要

本レポートは、電子設計自動化(EDA)ツール市場について、ツールタイプ、設計フロー段階、展開モード、エンドユーザー産業、および地域別にセグメント化し、その成長トレンドと予測を詳細に分析しています。市場規模は金額(USD)で提供され、2026年から2031年までの予測期間を対象としています。

市場規模と成長予測

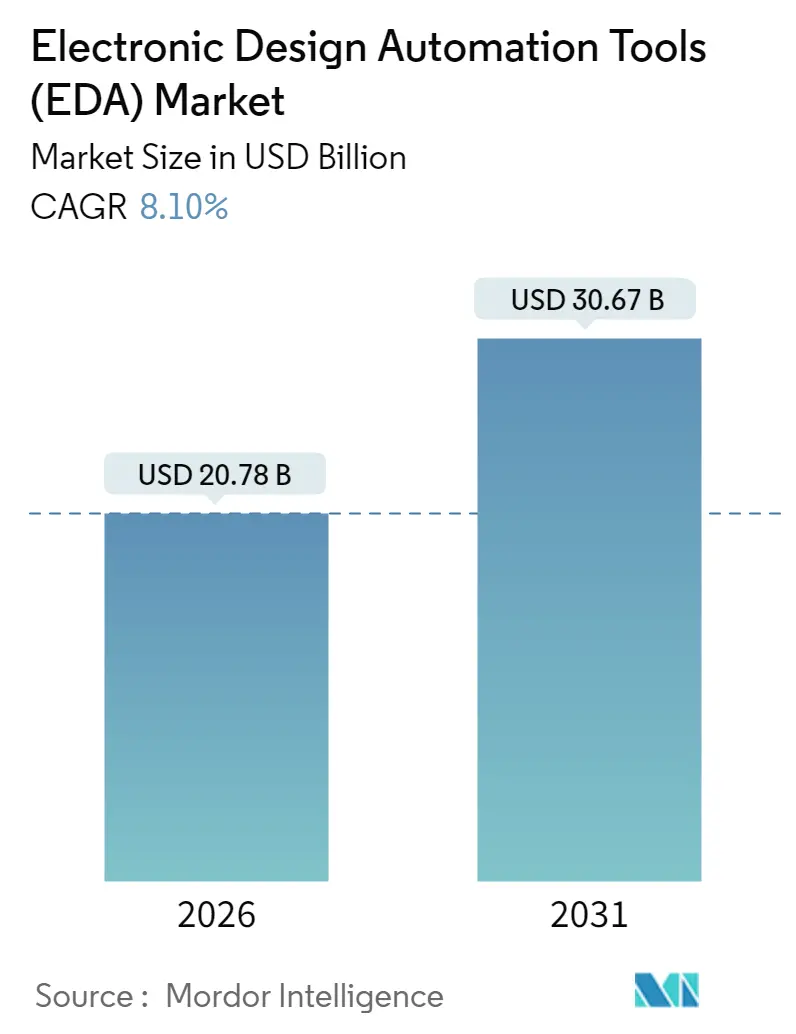

EDAツール市場は、2026年には207.8億米ドルと推定され、2025年の192.2億米ドルから成長し、2031年には306.7億米ドルに達すると予測されています。この期間における年平均成長率(CAGR)は8.10%と見込まれています。アジア太平洋地域が最も急速に成長し、最大の市場となることが予測されており、市場集中度は高いとされています。

この成長は、トランジスタのスケーリングの加速、AIを活用した設計フロー、ファウンドリとツールベンダー間の緊密な連携によって支えられています。チップ設計者は、手動によるルール調整からデータ駆動型の最適化へと移行しており、これによりテープアウトサイクルが短縮され、再スピンのリスクが低減されています。また、クラウドベースの容量バーストは高度な検証へのアクセスを広げ、自動車の機能安全要件は形式手法を主流の設計に押し上げています。2025年のSynopsysによるAnsysの350億米ドル規模の買収は、デバイスからシステムまでを統合し、シリコン、パッケージ、システム全体の性能を同時に最適化できるプラットフォームへの体系的な移行を示唆しています。一方で、地政学的な輸出規制は並行するEDAエコシステムを刺激し、ベンダーは複数の地域ファウンドリ向けにフローを認証し、収益の浸食を避けることを余儀なくされています。

主要な市場トレンドと洞察

成長要因

1. 先端ノードにおけるチップ密度の高まり:

Gate-All-Around(GAA)トランジスタ、背面電力供給、マルチダイパッケージングなどの技術により、7nmプロセスと比較して設計ルールチェックが10倍に増加しています。ファウンドリはEDAリーダーと共同でフローを開発しており、SynopsysとTSMCは2025年4月にA16およびN2Pノード向けの完全なデジタルおよびアナログツールチェーンを認証しました。これにより、高コストな再スピン(3nmでは1回あたり5000万米ドル以上)が削減されます。Intelの18Aプログラムも、コンピューティング、メモリ、I/Oを単一基板に統合する2.5D/3Dアーキテクチャ向けに統合されたフローに依存しています。

2. AI/MLアクセラレータとカスタムSoCの普及:

ハイパースケールおよびエッジプロバイダーは、目的別に構築された推論シリコンをますます委託しています。Cadenceは2025年第1四半期に半導体IP収益が前年比40%増を記録し、その勢いをAIおよびチップレットプロジェクトに起因しています。NVIDIA、ASML、TSMC、Synopsysは、CuLithoソフトウェアスタックを通じてリソグラフィシミュレーション速度を40倍に向上させ、AIのワットあたりの電力目標を満たすレチクルレイアウトを可能にしました。アクセラレータの異種性が高まるにつれて、SIPの再利用とオンパッケージ相互接続標準がIP検証の需要を強めています。

3. クラウドネイティブEDAワークフローの台頭(EDA-as-a-Service):

Synopsys Cloudは、ライセンスを持つツールがAWSやMicrosoft Azureにバーストして夜間にシミュレーション回帰を完了させ、重要なIPはセキュリティのためにオンプレミスに残すハイブリッドモデルを示しています。弾力的なスケーリングにより、アイドル状態のハードウェアが排除され、小規模な設計チームの検証スケジュールが数日短縮されます。しかし、2024年にはユーザーの70.5%が、輸出管理された設計や防衛契約におけるエアギャップ要件を理由に、ミッションクリティカルなフローをプライベートデータセンターに保持していました。それでも、ファブレススタートアップの増加は、従量課金制のコンピューティングを5nm設計への唯一の費用対効果の高い道と見なしています。

4. 車載ISO 26262機能安全要件への対応:

ISO 26262は、車両の寿命期間を通じてランダムなハードウェア故障が故障時間内(FIT)制限内に収まることを形式的に証明することを義務付けています。EDAベンダーは現在、故障キャンペーン自動化、安全ケース生成、ツール認定キットをバンドルしています。SynopsysのZ01XとSiemensのTessentは、形式分析と統合され、重要なブロックで90%を超える診断カバレッジを実証しています。ソフトウェア定義車両は検証の複雑さを増大させ、単一のドメインコントローラが複数のドライブバイワイヤサブシステムを監督します。規制当局は、RTLからゲートレベルネットリストまでの追跡可能な検証成果物を期待しており、認定されたフローの需要が高まっています。

5. オープンソースハードウェアの動き:

オープンソースハードウェアの動きが広がることで、検証の需要が高まっています。

6. 米中輸出規制による国内設計フローの加速:

米中間の輸出規制の二極化は、オンショア設計フローを加速させています。

阻害要因

1. 主要EDAスイートのライセンスコスト高騰:

包括的な3nmサインオフ向けの年間エンタープライズバンドルは、シートあたり100万米ドルを超えることがあり、中堅ファブはツールモジュールを優先し、リフレッシュサイクルを延長せざるを得ません。寡占的な供給により、特にオープンソースの代替品がないタイミングクロージャやリソグラフィシミュレーションパッケージにおいて、価格決定権はベンダーにあります。

2. サブ5nm物理設計エンジニアの人材不足:

米国半導体労働力開発法は、2028年までに67,000人の高度に専門化されたエンジニアの不足を予測しており、TSMCのアリゾナ工場も先端ノードのスタッフの現地化に苦戦しています。サブ5nmレイアウトには、電圧降下緩和、背面PDN、高度なパッケージングに関する専門知識が必要であり、これらは学部課程ではほとんどカバーされていません。ベンダーはAI駆動型設計アドバイザーを組み込み、立ち上げ時間を短縮していますが、それでも習熟には数年かかります。

3. クラウド展開におけるIP盗難およびサイバー侵入リスク:

クラウド展開におけるIP盗難およびサイバー侵入のリスクは、特に防衛分野で懸念が高まっています。

4. ムーアの法則の延長ペースの鈍化:

ムーアの法則の延長ペースが予想よりも遅いことは、ファウンドリのロードマップに影響を与えています。

セグメント分析

1. ツールタイプ別:

* IC物理設計および検証が2025年に35.82%の収益シェアを占め、リードしました。これは、すべてのテープアウトにおいて配置、ルーティング、静的タイミング、DRCが必須であるためです。しかし、AI強化型フロアプランニングは多目的最適化を自動化し、最近の3nm設計でターンアラウンドタイムを30%短縮しています。

* 半導体IP(SIP)は、ツールカテゴリの中で最速の9.7%のCAGRで拡大すると予測されています。これは、検証済みのインターフェースブロックや混合信号コアを好むチップレットアーキテクチャの台頭によるものです。2025年にはEDAツール市場収益の18.74%を占めましたが、ファウンドリが「既知の良品ダイ(known-good-die)」戦略を推進するにつれて、プロジェクトあたりのアタッチレートは2023年以降2倍になっています。

2. 設計フロー段階別:

* レイアウト、ルーティング、タイミングクロージャは、2025年にEDAツール市場規模の32.10%を占めました。これは、サインオフ品質のタイミング収束と高度な3D寄生抽出の不可欠な性質を反映しています。

* フロントエンド設計RTLツールは、2031年まで9.35%の最速CAGRを記録すると予測されています。これは、高レベル合成(HLS)や自然言語からRTLへのジェネレータが生産性を向上させているためです。AI支援コード生成により、機能意図をより少ない反復で捉えることができるため、RTL自動化の市場規模は2031年までに大幅に成長すると予測されています。

3. 展開モード別:

* オンプレミスインストールは2025年に69.60%の収益を占めましたが、クラウドの受け入れが進むにつれてこの数字は徐々に減少しています。セキュリティを重視するセクターは、重要なRTL、ネットリスト、サインオフデッキをローカルデータセンターに保持していますが、回帰スイープのために検証ワークロードをクラウドにバーストさせます。

* クラウドベースのフローは、新興のファブライト地域でのツールアクセス性を向上させ、一部のスタートアップは同等のハードウェアをリースするよりも40%のコスト削減を報告しています。クラウド展開に起因するEDAツール市場規模は、プロジェクトのマイルストーンと費用を一致させるサブスクリプションライセンスによって、2031年までに大幅に成長すると予測されています。

4. エンドユーザー産業別:

* 自動車およびモビリティは9.85%のCAGRを示し、ゾーンアーキテクチャと自動運転スタックが新たな機能安全検証を義務付けるため、他のすべての垂直市場を上回っています。ISO 26262 ASIL-Dコントローラは、RTL、ゲート、トランジスタビュー全体で網羅的な故障カバレッジを文書化する必要があり、インフォテインメントプロセッサと比較してシミュレーションベクトル数を3倍にしています。

* 通信インフラは2025年に26.55%と最大のシェアを維持しましたが、5Gマクロ展開が成熟するにつれて成長は鈍化しています。電気自動車のパワートレインやADASチップも、デジタル制御ループとアナログセンサーインターフェースを橋渡しする混合信号検証の需要を刺激しています。

地域分析

1. アジア太平洋:

2025年に42.05%のシェアを占め、2031年までに9.55%のCAGRで成長します。台湾と韓国のファウンドリ集積が地域のツール需要を支え、中国は米国の輸出規制に対応して国産EDAスタックを加速させています。国家主導のイニシアチブは、AI支援の配置・配線エンジンやSPICEシミュレータに補助金を投入し、3nm生産が本格化する前にフローの現地化を目指しています。インドは大規模なエンジニアリング基盤を活用し、2024年には設計サービス企業が17%成長しました。

2. 北米:

AIアルゴリズム、IPカタログ、クラウドインフラにおけるリーダーシップを通じて影響力を維持しています。2025年にはシェアが29.15%にわずかに縮小しましたが、最先端ノード向けの参照ツールフローの主要な供給源であり続けています。輸出管理体制はベンダーにライセンスキーのジオフェンシングを義務付け、コンプライアンスコストを増加させますが、北米のIPチェーンを固定化する効果もあります。Intel FoundryとSynopsysの18A認定フローに関する協力は、米国が先端製造シェアを取り戻すための取り組みを強化しています。

3. 欧州:

自動車および産業用途に焦点を当てており、ISO 26262がプレミアム検証ツールの採用を推進しています。TSMCの2025年ミュンヘン設計センター開設は、ファウンドリエンジニアを地域サプライチェーンに組み込み、3D-ICパッケージングや電力効率の高いAIアクセラレータの直接的なサポートを提供することを目指しています。EUチップス法は、電子設計クラスター向けのR&D税額控除を重視し、地域のEDA採用をさらに刺激しています。

4. 中東・アフリカおよび南米:

まだ初期段階ですが、政府のファブプロジェクトやIoT展開が出現する地域では2桁成長を示しています。

競争環境

市場は寡占的な集中を示しており、Synopsys、Cadence、Siemensがエンドツーエンドのスイートと深いファウンドリ認証パイプラインを通じて収益の大部分を支配しています。Synopsysによる2025年7月のAnsysの350億米ドル規模の買収完了は、半導体サインオフ、CFD、熱、機械シミュレーションを単一環境に融合させ、デバイスからシステムまでを垂直統合した初の設計スタックを創出しました。Cadenceは、システムペルソナに最適化されたIPで製品を調整し、生成AIを活用して戦略的な配置を行っています。Siemensは、産業用ソフトウェア部門のデジタルツインの利点を活用し、検証プロセスを工場シミュレーションにまで拡大し、スマート製造クライアントのニーズに応えています。

地域チャレンジャーは、主権要件に焦点を当てています。中国の国営ツールベンダーは、14nm車載コントローラ向けのパイロットテープアウトを確保し、2026年までに7nm認証を計画しています。性能ギャップは残るものの、バンドルされた補助金と強制的な国内ツール割り当てにより、現地プロジェクトでのシェアは増加しています。主に米国のスタートアップであるクラウドネイティブなディスラプターは、ブラウザベースの回路図キャプチャとPCB共同シミュレーションを提供し、ティア1のEDAスイートに見過ごされているメーカーや中規模OEMをターゲットにしています。しかし、認定された3nmフローの欠如は、最先端市場への浸透を制限しています。

ファウンドリとの提携は依然として極めて重要です。TSMCの3DFabric AllianceやSamsung SAFEプログラムへの参加は、パートナーに早期の設計ルール可視性と共同マーケティングの機会を与えます。デイゼロのプロセス設計キット(PDK)の可用性を保証できないツールサプライヤーは、高収益の初期テープアウトから排除されるリスクがあります。したがって、競争の物語は、ツールの機能よりも、エコシステムの広さ、IPカタログの規模、クラウドとオンプレミス環境全体でのスケーラビリティによって推進されています。

主要企業

* ANSYS Inc.

* Cadence Design Systems Inc.

* Keysight Technologies Inc.

* Synopsys Inc.

* Xilinx Inc.

最近の業界動向

* 2025年7月: SynopsysはAnsysの350億米ドル規模の買収を完了し、EDA、マルチフィジックス、機械シミュレーションを網羅するチップからシステムまでの設計の強力な企業を形成しました。

* 2025年5月: TSMCはミュンヘンに設計センターを開設し、欧州の顧客とAIおよび車載チップを共同開発しました。

* 2025年4月: SynopsysとIntel Foundryは、マルチダイパッケージングサポートを含む18A技術向けの生産準備が整ったデジタルおよびアナログフローをリリースしました。

* 2025年4月: Cadenceは2025年第1四半期の収益が12.42億米ドルであったと発表し、AIおよびチップレット向けのIP需要により通期ガイダンスを引き上げました。

このレポートは、世界の電子設計自動化(EDA)ツール市場に関する詳細な分析を提供しています。EDAツールは、コンピューターの支援を受けて電子システムを設計するためのソフトウェア製品であり、回路基板、プロセッサ、および様々な複雑な電子機器の設計に不可欠です。手動による設計方法に代わり、半導体や回路基板の設計において広く利用されています。

市場の概要と予測

EDAツール市場は、2026年から2031年にかけて年平均成長率(CAGR)8.1%で拡大し、2031年には306.7億米ドルに達すると予測されています。

市場の主要な推進要因には、以下の点が挙げられます。

* 先進ノードにおけるチップ密度の高まり

* AI/MLアクセラレーターやカスタムSoCの普及

* クラウドネイティブなEDAワークフロー(EDA-as-a-Service)の台頭

* 自動車分野におけるISO 26262機能安全コンプライアンスの必要性

* オープンソースハードウェアの動きの活発化による検証需要の増加

* 米中間の輸出規制の二極化によるオンショア設計フローの加速

一方、市場の抑制要因としては、以下の点が指摘されています。

* 主要なEDAスイートのライセンスコストの高騰

* サブ5nm物理設計エンジニアの人材不足

* クラウド展開におけるIP盗難やサイバー侵入のリスク

* ムーアの法則の延長ペースの鈍化

主要な調査結果

* 地域別成長率: アジア太平洋地域が最も速い成長を遂げると見込まれており、ファウンドリの集積と国家主導のツールプログラムに支えられ、2031年までのCAGRは9.55%と予測されています。

* ツールタイプ別成長率: 半導体IP(SIP)が最も高いCAGR 9.7%を記録すると予測されています。これは、チップレットやヘテロジニアス統合プロジェクトの増加によるものです。

* 自動車設計の需要: ISO 26262安全規制により、徹底的な形式検証が求められるため、自動車およびモビリティ分野でのツール支出はCAGR 9.85%で増加しています。

* クラウド利用の影響: クラウドネイティブなワークフローは検証のターンアラウンドタイムを短縮し、設備投資を削減しますが、IPの機密性から、依然として69.60%のフローがオンプレミスで実行されています。

* 主要企業: Synopsys、Cadence、Siemensの3社が世界の収益の約70%を占めており、ファウンドリ認定フローと広範なIPカタログによってその地位を強化しています。

レポートの分析範囲

本レポートでは、市場を以下の観点から詳細に分析しています。

* ツールタイプ別: コンピューター支援エンジニアリング(CAE)、IC物理設計と検証、PCBおよびマルチチップモジュール(MCM)、半導体IP(SIP)、サービス。

* 設計フロー段階別: フロントエンド設計(RTL)、ロジック合成と機能検証、レイアウト・ルーティングとタイミングクロージャ、サインオフ(DFM、パワー、SI、熱)。

* 展開モード別: オンプレミス、クラウドベース。

* エンドユーザー産業別: 通信インフラ、家電、自動車およびモビリティ、産業およびエネルギー、航空宇宙および防衛、医療機器、その他産業。

* 地域別: 北米、南米、欧州、アジア太平洋、中東、アフリカ。

競争環境

市場集中度、戦略的動向、市場シェア分析、およびAnsys Inc.、Cadence Design Systems Inc.、Synopsys Inc.、Siemens Digital Industries Software(Mentor Graphics)など主要20社の企業プロファイルが詳細に記述されています。

その他の分析

バリューチェーン分析、規制環境、技術的展望、ポーターのファイブフォース分析、投資分析、マクロ経済要因が市場に与える影響、市場機会と将来の展望についても網羅されています。

1. はじめに

- 1.1 調査の前提と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

- 4.2 市場の推進要因

- 4.2.1 先端ノードにおけるチップ密度の高騰

- 4.2.2 AI/MLアクセラレータとカスタムSoCの普及

- 4.2.3 クラウドネイティブEDAワークフロー(EDA-as-a-Service)の台頭

- 4.2.4 自動車向けISO 26262機能安全コンプライアンスの必要性

- 4.2.5 オープンソースハードウェアの動きの拡大が検証需要を促進

- 4.2.6 米中輸出管理の二極化がオンショア設計フローを加速

- 4.3 市場の阻害要因

- 4.3.1 主要なEDAスイートのライセンスコストの高騰

- 4.3.2 5nm以下の物理設計エンジニアの人材不足

- 4.3.3 クラウド展開におけるIP盗難およびサイバー侵入のリスク

- 4.3.4 ムーアの法則のペースの延長が予想より遅いこと

- 4.4 バリューチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

- 4.7 ポーターの5つの力分析

- 4.7.1 供給者の交渉力

- 4.7.2 買い手の交渉力

- 4.7.3 新規参入の脅威

- 4.7.4 代替品の脅威

- 4.7.5 競争の激しさ

- 4.8 投資分析

- 4.9 マクロ経済要因が市場に与える影響

5. 市場規模と成長予測(金額)

- 5.1 ツールタイプ別

- 5.1.1 コンピューター支援エンジニアリング (CAE)

- 5.1.1 IC物理設計と検証

- 5.1.3 PCBおよびマルチチップモジュール (MCM)

- 5.1.4 半導体知的財産 (SIP)

- 5.1.5 サービス

- 5.2 設計フロー段階別

- 5.2.1 フロントエンド設計 (RTL)

- 5.2.2 論理合成と機能検証

- 5.2.3 レイアウト、ルーティング、タイミングクロージャ

- 5.2.4 サインオフ (DFM、電力、SI、熱)

- 5.3 展開モード別

- 5.3.1 オンプレミス

- 5.3.2 クラウドベース

- 5.4 エンドユーザー産業別

- 5.4.1 通信インフラ

- 5.4.2 家庭用電化製品

- 5.4.3 自動車およびモビリティ

- 5.4.4 産業およびエネルギー

- 5.4.5 航空宇宙および防衛

- 5.4.6 医療機器

- 5.4.7 その他の産業

- 5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 南米のその他の地域

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 ヨーロッパのその他の地域

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 韓国

- 5.5.4.4 インド

- 5.5.4.5 アジア太平洋のその他の地域

- 5.5.5 中東

- 5.5.5.1 サウジアラビア

- 5.5.5.2 アラブ首長国連邦

- 5.5.5.3 中東のその他の地域

- 5.5.6 アフリカ

- 5.5.6.1 南アフリカ

- 5.5.6.2 アフリカのその他の地域

6. 競合情勢

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

- 6.4 企業プロファイル (グローバルレベルの概要、市場レベルの概要、主要セグメント、財務、戦略情報、市場ランキング/シェア、製品とサービス、最近の動向を含む)

- 6.4.1 Ansys Inc.

- 6.4.2 Cadence Design Systems Inc.

- 6.4.3 Synopsys Inc.

- 6.4.4 Siemens Digital Industries Software (Mentor Graphics)

- 6.4.5 Keysight Technologies Inc.

- 6.4.6 Altium Limited

- 6.4.7 Zuken Ltd.

- 6.4.8 Xilinx Inc. (AMD Adaptive and Embedded Computing Group)

- 6.4.9 Aldec Inc.

- 6.4.10 Agnisys Inc.

- 6.4.11 Lauterbach GmbH

- 6.4.12 Silvaco Inc.

- 6.4.13 Real Intent Inc.

- 6.4.14 Axiomise Ltd.

- 6.4.15 Imperas Software Ltd.

- 6.4.16 PDF Solutions Inc.

- 6.4.17 Flex Logix Technologies Inc.

- 6.4.18 Andes Technology Corp.

- 6.4.19 Cobham Gaisler AB

- 6.4.20 Arteris Inc.

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

電子設計自動化(EDA)ツールは、集積回路(IC)、プリント基板(PCB)、フィールドプログラマブルゲートアレイ(FPGA)などの電子システムの設計、検証、製造を自動化し、最適化するためのソフトウェアおよびハードウェアツールの総称でございます。現代の電子機器は、その機能と複雑性が飛躍的に増大しており、手作業による設計では時間、コスト、品質の面で限界があります。EDAツールは、この複雑な設計プロセスを効率化し、設計ミスを削減し、市場投入までの時間を短縮するために不可欠な存在となっております。

EDAツールは、その用途に応じて多岐にわたる種類が存在します。まず、集積回路(IC)設計においては、論理合成ツールがハードウェア記述言語(HDL)で記述された設計をゲートレベルのネットリストに変換します。その後、配置配線(Place & Route)ツールが、数百万から数十億個に及ぶゲートやトランジスタを物理的にチップ上に配置し、それらを接続する配線を最適化します。静的タイミング解析(Static Timing Analysis: STA)ツールは、設計された回路が所定の速度で動作するかを検証し、物理検証(Physical Verification)ツールは、設計ルールチェック(DRC)やレイアウト対回路図(LVS)チェックを通じて、製造上の制約や回路図との整合性を確認します。回路シミュレーションツール(例:SPICE、FastSPICE)は、アナログ回路やミックスドシグナル回路の電気的特性を詳細に解析します。また、形式検証(Formal Verification)ツールは、数学的な手法を用いて設計の機能的な正しさを厳密に証明し、テスト容易化設計(Design for Testability: DFT)ツールは、製造後のテストを容易にするための回路を組み込みます。

プリント基板(PCB)設計においては、回路図入力(Schematic Capture)ツールが電子回路の論理的な接続を定義し、レイアウトツールが部品の配置と配線を物理的に行います。高速信号の増加に伴い、信号完全性(Signal Integrity: SI)や電源完全性(Power Integrity: PI)解析ツールが、信号の劣化や電源ノイズの問題を事前に特定し解決するために重要です。さらに、熱解析ツールは、高密度な基板における放熱問題を評価します。FPGA設計においては、HDL合成、配置配線、シミュレーションといったIC設計と類似したプロセスが、FPGAベンダーが提供する専用のEDAツールスイート内で実行されます。システムレベル設計ツールは、より抽象度の高いレベルでシステム全体のアーキテクチャを検討し、高位合成(High-Level Synthesis: HLS)ツールは、C/C++などの高水準言語からハードウェア記述言語を自動生成することで、設計期間の大幅な短縮に貢献します。

EDAツールの主な用途は、電子システムの設計ライフサイクル全体をカバーします。具体的には、まず仕様に基づいた概念設計から始まり、ハードウェア記述言語(HDL)を用いた機能設計が行われます。次に、論理合成によってゲートレベルのネットリストが生成され、物理設計段階でチップや基板上への配置配線が行われます。この各段階で、シミュレーション、検証、解析ツールが繰り返し使用され、設計の機能性、性能、信頼性、製造可能性が確認されます。最終的に、製造データ(GDSIIファイルなど)が生成され、半導体ファウンドリや基板メーカーに引き渡されます。EDAツールは、この一連のプロセスにおいて、設計の自動化、最適化、エラー検出、そして設計品質の向上を実現し、結果として開発期間の短縮とコスト削減に大きく貢献しています。

関連技術としては、まずクラウドコンピューティングが挙げられます。EDAワークロードは計算リソースを大量に消費するため、クラウドの柔軟なスケーラビリティとオンデマンドのリソース提供は、特に大規模なシミュレーションや検証において非常に有効です。次に、人工知能(AI)と機械学習(ML)は、設計空間探索、最適化、検証の高速化、設計ルールの自動生成、さらには設計プロセスの自律化といった分野で活用が進んでいます。高性能計算(HPC)は、複雑な物理シミュレーションや大規模な並列処理を必要とするEDAタスクの基盤技術です。また、デジタルツイン技術は、物理的なシステムを仮想空間で忠実に再現し、EDAツールと連携してシステムレベルでの挙動予測や検証を可能にします。サイバーセキュリティは、設計IP(知的財産)の保護や、設計される電子システム自体のセキュリティ確保という点で、EDAプロセス全体にわたって重要な考慮事項となっています。

EDA市場は、Synopsys、Cadence Design Systems、Siemens EDA(旧Mentor Graphics)の3社が主要なプレイヤーとして市場の大部分を占める寡占状態にあります。この市場は、IoT、AI、5G通信、自動運転、データセンターといった先端技術の進化と、それに伴う半導体需要の拡大によって持続的に成長しています。特に、より微細なプロセスノードへの移行や、システムオンチップ(SoC)の複雑化、異種統合(Heterogeneous Integration)の進展が、より高度なEDAツールの必要性を高めています。設計IPの再利用も、開発期間短縮とコスト削減の観点から重要性を増しており、EDAベンダーはIPプロバイダーとの連携や自社でのIP提供も強化しています。

将来展望として、EDAツールはさらなる複雑化と高度化が予測されます。まず、3nm、2nmといった先端プロセスノードにおける量子効果やばらつきへの対応は、物理設計および検証ツールにとって大きな課題です。AI/MLの統合はさらに深化し、設計の最適化、検証の効率化、さらには設計プロセスの自律化(Autonomous Design)へと進化していくでしょう。これにより、設計者はより高次の抽象度で設計に集中できるようになります。クラウドネイティブEDAへの移行も加速し、設計チーム間のコラボレーション強化、リソースの柔軟な利用、そしてセキュリティの向上が期待されます。また、システムレベルでの設計と検証の重要性が増しており、マルチダイ統合や3D-ICといった異種統合技術に対応するツールが不可欠となります。セキュリティバイデザインの概念がEDAプロセスに早期から組み込まれ、設計段階で潜在的な脆弱性を特定し対処する動きも活発化するでしょう。オープンソースEDAの動きも一部で見られますが、商用ツールの高度な機能とサポートが引き続き市場を牽引すると考えられます。これらの進化を通じて、EDAツールは未来の電子技術革新を支える基盤であり続けるでしょう。