SRAMおよびROMデザインIP市場 規模・シェア分析 – 成長トレンドと予測 (2025年~2030年)

SRAMおよびROMデザインIP市場レポートは、メモリタイプ (SRAM、ROMなど)、アプリケーション (家電、電気通信およびネットワーキングなど)、テクノロジーノード (14nm以下、15-22nm、28-40nm、45nm以上)、IPデリバリータイプ (ハードIP、ソフトIPなど)、および地域 (北米、南米、ヨーロッパ、アジア太平洋、中東、アフリカ) 別に分類されます。市場予測は、金額 (米ドル) で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

SRAMおよびROMデザインIP市場は、2025年から2030年にかけて緩やかながらも着実な成長が見込まれています。本レポートは、メモリタイプ、アプリケーション、テクノロジーノード、IP提供タイプ、および地域別に市場を詳細に分析し、2030年までの成長トレンドと予測を提供しています。

市場概要

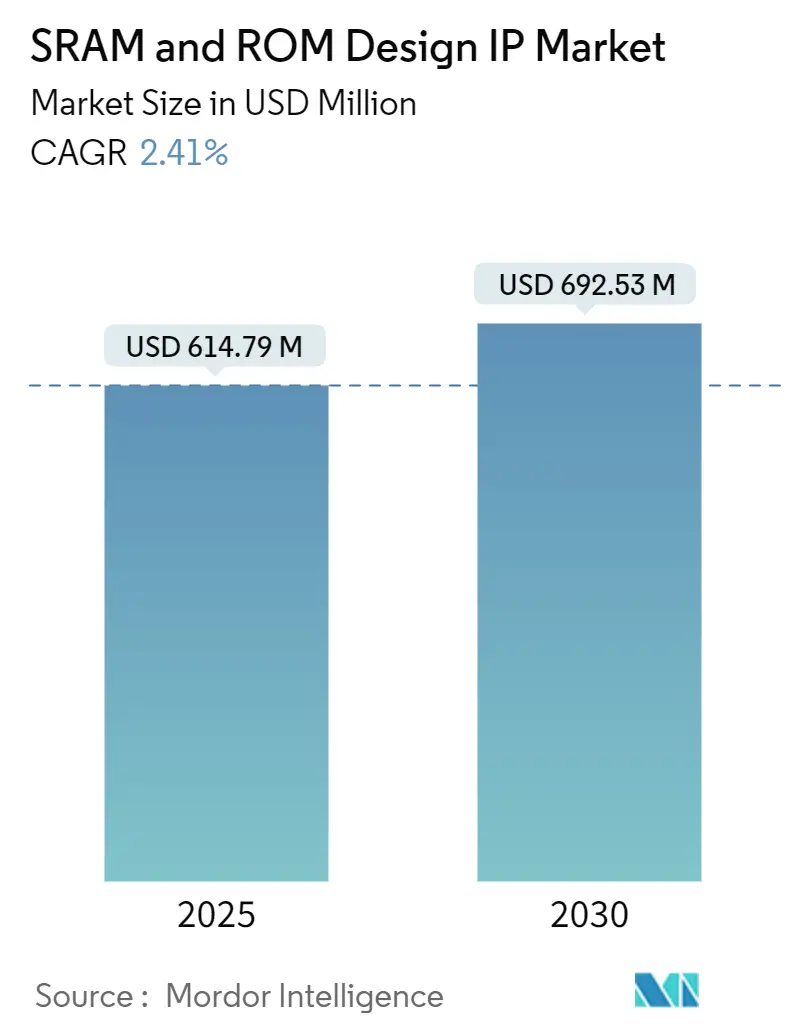

SRAMおよびROMデザインIP市場は、2025年には6億1,479万米ドルと評価され、2030年には6億9,253万米ドルに達すると予測されており、予測期間中の年平均成長率(CAGR)は2.41%です。この成長は、キャッシュ密度の高いAIアクセラレータ、5Gエッジノード、および車載機能安全プラットフォームに対する継続的な需要に支えられています。特に14nm以下のプロセスでは、ばらつき、リーク電流、ソフトエラー率を抑制するビットセルアーキテクチャが求められるため、不釣り合いに高いライセンス料が発生しています。IP提供形式としては、資格認定リスクを最小限に抑え、テープアウトスケジュールを加速させるハードIPが依然として好まれていますが、ヘテロジニアスパッケージングが量産段階に入るにつれて、チップレット対応のメモリタイルが勢いを増しています。オープンソースコンパイラが平均販売価格(ASP)を押し下げているため、競争は激化しており、既存ベンダーは検証スイートとファウンドリパートナーシップに注力しています。これにより、顧客はより信頼性の高いIPを選択し、設計リスクを低減することができます。また、AI、IoT、自動車などの新興アプリケーションにおける高性能・低消費電力の要求が高まるにつれて、SRAMおよびROMデザインIPの重要性はさらに増しています。特に、エッジAIデバイスや自動運転システムでは、リアルタイム処理と高い信頼性が不可欠であり、これらを支えるメモリIPの進化が期待されています。

主要な市場プレーヤーは、Arm、Cadence Design Systems、Rambus、Synopsys、Dolphin Design、Menta、Surecore、Virage Logic (Synopsysに買収)、eMemory Technology、Kilopass Technology (Synopsysに買収) などです。これらの企業は、技術革新、戦略的パートナーシップ、M&Aを通じて市場での競争力を維持・強化しています。例えば、Armは低消費電力と高性能を両立させるための新しいメモリIPソリューションを継続的に開発しており、Synopsysは広範なIPポートフォリオとファウンドリとの強固な連携により、顧客の多様なニーズに応えています。

地域別に見ると、アジア太平洋地域がSRAMおよびROMデザインIP市場において最大のシェアを占めており、特に中国、韓国、台湾における半導体製造と設計活動の活発化が市場成長を牽引しています。北米と欧州も、AI、データセンター、自動車分野での技術革新と投資により、堅調な成長が見込まれています。

市場の課題としては、高度なプロセスノードにおける設計の複雑性の増大、IPの検証と統合にかかる時間とコスト、そしてオープンソースIPの台頭による価格競争の激化が挙げられます。しかし、これらの課題は、より高度な設計自動化ツール、標準化されたインターフェース、そしてIPベンダーとファウンドリ間の緊密な協力によって克服されつつあります。

結論として、SRAMおよびROMデザインIP市場は、AI、5G、IoT、自動車といったメガトレンドに支えられ、今後も安定した成長を続けると予測されます。技術革新と戦略的パートナーシップが、このダイナミックな市場における成功の鍵となるでしょう。

このレポートは、グローバルSRAMおよびROMデザインIP市場に焦点を当て、その動向、提供されるIPの種類、全体的な市場シナリオ、主要ベンダーを詳細に分析しています。また、MRAM技術についても、収益、技術トレンド、最新の開発状況、アプリケーション(スタンドアロンと組み込み)、技術ノードと主要ベンダーのロードマップの観点から包括的に分析しています。

市場規模に関して、SRAMおよびROMデザインIP市場は2025年に6億1,479万米ドルに達し、2030年までに6億9,253万米ドルに成長すると予測されています。

市場の主要な推進要因としては、以下の点が挙げられます。

* AI中心のSoCの普及に伴う大規模なオンチップキャッシュの需要増加。

* 5Gおよびエッジコンピューティングの展開による低電力組み込みSRAMの採用加速。

* 28nm以下のプロセスにおけるeFlashからMRAMへの移行が新たなライセンス収益源を創出。

* 車載グレード1の機能安全規制が、認定メモリIPの需要を押し上げていること。

* チップレットアーキテクチャの標準化が、ダイ間メモリIPの要件を確立していること。

* ファウンドリのターンキーメモリコンパイラプログラムが、ファブレス企業の市場投入までの時間を短縮していること。

一方、市場の抑制要因としては、以下の課題が指摘されています。

* オープンソースのメモリコンパイラによる価格競争が平均販売価格(ASP)を低下させていること。

* 新興のReRAM/FeRAM代替品が、小規模なROM IPソケットを侵食していること。

* 中国でのテープアウトに対する輸出管理規制の遵守が障壁となっていること。

* 7nm以下のSRAMビットセルの信頼性に関する課題が、認定コストを増加させていること。

レポートでは、市場はメモリタイプ別(SRAM、ROM、MRAM、組み込みフラッシュ/その他のNVM)、アプリケーション別(家電、通信・ネットワーキング、自動車・輸送、産業・IoT、航空宇宙・防衛など)、技術ノード別(14nm以下、15-22nm、28-40nm、45nm以上)、IP提供タイプ別(ハードIP、ソフトIP、パラメータ化コンパイラIP、チップレット/3DダイレベルIP)、および地域別(北米、南米、欧州、アジア太平洋、中東、アフリカ)に詳細に分析されています。

特に、組み込みフラッシュおよびその他の不揮発性メモリIPは、IoTおよび自動車需要に牽引され、2030年まで年平均成長率3.8%で最も速い成長を遂げると見込まれています。地域別では、アジア太平洋地域がファウンドリ規模、政府補助金、設計拠点の集中により、市場シェアの47.31%を占め、年平均成長率3.9%で持続的な成長を続けると予測されています。

チップレットのトレンドはメモリIP市場を再形成しており、UCIeリンクと組み合わせたチップレット対応メモリタイルは、異なるノード選択を可能にし、帯域幅を向上させるため、年平均成長率4.3%で成長しています。価格圧力は、オープンソースSRAMコンパイラや大学が支援するライブラリによってエントリーレベルのASPが低下しているため、商業ベンダーは電力効率、安全性、検証の深さに重点を置くことを余儀なくされています。

また、2022年に課された米国による高度なSRAMおよび新興メモリIPに対する輸出管理規制は、中国を拠点とする設計に影響を与え、取引サイクルを長期化させ、国内代替品の開発を促進しています。

競争環境については、市場集中度、戦略的動向、市場シェア分析が行われ、Arm Ltd.、Synopsys Inc.、Cadence Design Systems Inc.、Siemens EDAなどの主要ベンダーのプロファイルが提供されています。

このレポートは、市場の機会と将来の展望についても評価し、未開拓の分野や満たされていないニーズを特定しています。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

-

4.2 市場の推進要因

- 4.2.1 大規模なオンチップキャッシュを要求するAI中心のSoCの普及

- 4.2.2 5Gおよびエッジコンピューティングの展開が低消費電力組み込みSRAMの採用を加速

- 4.2.3 28 nm以下のeFlashからMRAMへの移行が新たなライセンス収益源を創出

- 4.2.4 車載グレード1の機能安全規則が認定メモリIPの需要を促進

- 4.2.5 チップレットアーキテクチャがダイ間メモリIP要件を標準化

- 4.2.6 ファウンドリのターンキーメモリコンパイラプログラムがファブレス企業の市場投入期間を短縮

-

4.3 市場の阻害要因

- 4.3.1 オープンソースメモリコンパイラからの価格圧力によるASPの低下

- 4.3.2 新興のReRAM/FeRAM代替品が小型ROM IPソケットを侵食

- 4.3.3 中国のテープアウトにおける輸出管理コンプライアンスの課題

- 4.3.4 7 nm以下のSRAMビットセルにおける信頼性の逆風が認定コストを増大

- 4.4 業界エコシステム分析

- 4.5 マクロ経済要因の影響

- 4.6 技術的展望

-

4.7 ポーターの5つの力分析

- 4.7.1 新規参入者の脅威

- 4.7.2 サプライヤーの交渉力

- 4.7.3 買い手の交渉力

- 4.7.4 代替品の脅威

- 4.7.5 競争上の対抗関係

5. 市場規模と成長予測(金額)

-

5.1 メモリタイプ別

- 5.1.1 SRAM

- 5.1.2 ROM (PROM / EPROM / EEPROM)

- 5.1.3 MRAM

- 5.1.4 組み込みフラッシュ / その他のNVM

-

5.2 アプリケーション別

- 5.2.1 家庭用電化製品

- 5.2.2 電気通信およびネットワーキング

- 5.2.3 自動車および輸送

- 5.2.4 産業およびIoT

- 5.2.5 航空宇宙および防衛

- 5.2.6 その他のアプリケーション

-

5.3 テクノロジーノード別

- 5.3.1 ≤14 nm

- 5.3.2 15 – 22 nm

- 5.3.3 28 – 40 nm

- 5.3.4 ≥45 nm

-

5.4 IPデリバリータイプ別

- 5.4.1 ハードIP

- 5.4.2 ソフトIP

- 5.4.3 パラメータ化コンパイラIP

- 5.4.4 チップレット / 3DダイレベルIP

-

5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米地域

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 スペイン

- 5.5.3.6 その他のヨーロッパ地域

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 インド

- 5.5.4.4 韓国

- 5.5.4.5 東南アジア

- 5.5.4.6 その他のアジア太平洋地域

- 5.5.5 中東

- 5.5.5.1 サウジアラビア

- 5.5.5.2 アラブ首長国連邦

- 5.5.5.3 トルコ

- 5.5.5.4 その他の中東地域

- 5.5.6 アフリカ

- 5.5.6.1 南アフリカ

- 5.5.6.2 ナイジェリア

- 5.5.6.3 その他のアフリカ地域

6. 競合情勢

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

-

6.4 企業プロファイル(グローバルレベルの概要、市場レベルの概要、主要セグメント、利用可能な財務情報、戦略情報、主要企業の市場ランク/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 Arm Ltd.

- 6.4.2 Synopsys Inc.

- 6.4.3 Cadence Design Systems Inc.

- 6.4.4 Siemens EDA (Mentor Graphics Corporation)

- 6.4.5 eMemory Technology Inc.

- 6.4.6 Silvaco Inc.

- 6.4.7 Dolphin Design SAS

- 6.4.8 VeriSilicon Holdings Co. Ltd.

- 6.4.9 SureCore Ltd.

- 6.4.10 Xilinx Inc.

- 6.4.11 Renesas Electronics Corporation

- 6.4.12 Everspin Technologies Inc.

- 6.4.13 Avalanche Technology Inc.

- 6.4.14 TDK Corporation

- 6.4.15 Kilopass Technology Inc.

- 6.4.16 Silicon Storage Technology Inc.

- 6.4.17 GSI Technology Inc.

- 6.4.18 Dolphin Technology Inc.

- 6.4.19 TekStart LLC

- 6.4.20 Flex Logix Technologies Inc.

- 6.4.21 Rambus Inc.

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

SRAMおよびROMデザインIPは、半導体設計において極めて重要な役割を果たす知的財産(IP)であり、現代のあらゆる電子機器の基盤を支えています。IPとは、特定の機能を持つ回路ブロックをあらかじめ設計・検証し、再利用可能な形で提供されるもので、これにより半導体メーカーは開発期間の短縮、コスト削減、設計リスクの低減を実現できます。SRAM(Static Random Access Memory)は、電源が供給されている間はデータを保持し続ける揮発性メモリであり、高速アクセスが特徴です。一方、ROM(Read-Only Memory)は、電源を切ってもデータを保持する不揮発性メモリで、一度書き込まれたデータは基本的に読み出し専用となります。これらのメモリをIPとして提供することで、SoC(System-on-a-Chip)などの複雑な半導体製品に効率的に組み込むことが可能になります。

SRAMデザインIPには、その用途に応じて多種多様なタイプが存在します。例えば、CPUやGPUのキャッシュメモリとして使われる高速・低レイテンシを追求したタイプ、モバイル機器やIoTデバイス向けに消費電力を極限まで抑えた低消費電力タイプ、複数のポートから同時にアクセス可能なマルチポートSRAM、そして特定のアプリケーションに最適化された高密度SRAMなどがあります。これらは、シングルポート、デュアルポート、またはそれ以上のポート構成を持つことができ、データアクセス要件に応じて選択されます。また、テスト容易性設計(DFT)の一環として、組み込み型メモリBIST(MBIST)回路を内蔵し、製造テストやフィールドでの診断を効率化する機能を持つものも一般的です。プロセス技術の進化に伴い、FinFETやGAA(Gate-All-Around)などの先端プロセスに最適化されたSRAM IPも提供されており、より高い性能と電力効率を実現しています。

ROMデザインIPもまた、その特性と用途に応じていくつかの種類に分類されます。最も基本的なものはマスクROMで、製造時にデータが書き込まれ、その後は変更できません。大容量かつ低コストで提供できるため、大量生産される製品のファームウェアやブートコードなどに利用されます。次に、OTP(One-Time Programmable)ROMがあり、これはユーザーが一度だけデータを書き込むことができるタイプです。eFuseやアンチヒューズといった技術が用いられ、デバイスのID、セキュリティキー、キャリブレーションデータなどの格納に適しています。さらに、MTP(Multi-Time Programmable)ROMは、限定的な回数であればデータの書き換えが可能なタイプで、ファームウェアのマイナーアップデートなどに利用されることがあります。厳密にはROMではありませんが、組み込みシステムではNORフラッシュメモリがブートコードや設定データの格納に広く用いられ、ROMと同様の役割を果たすことも多いです。これらのROM IPは、不揮発性メモリとして、システムの起動に必要な情報や変更されることのない固定データを安全に保持するために不可欠です。

これらのSRAMおよびROMデザインIPは、幅広い分野で活用されています。SRAM IPは、CPUやGPUのL1、L2、L3キャッシュメモリとして、またネットワーク機器のバッファメモリ、AIアクセラレータの高速データストレージ、マイクロコントローラのスクラッチパッドメモリなど、高速なデータアクセスが求められるあらゆる場面で利用されます。一方、ROM IPは、マイクロコントローラやSoCのブートコード、ファームウェア、デバイスのシリアル番号やセキュリティキー、キャリブレーションデータ、ルックアップテーブル(LUT)など、システムが動作するために不可欠な固定情報の格納に用いられます。特に、IoTデバイスや車載システムでは、低消費電力と高い信頼性が求められるため、これらのメモリIPの選定はシステムの性能と安定性を大きく左右します。

関連技術としては、まず半導体製造プロセス技術の進化が挙げられます。7nm、5nm、3nmといった微細化されたプロセスノードでは、メモリセルのサイズが縮小され、より高密度で低消費電力、高速なメモリIPが実現されます。また、EDA(Electronic Design Automation)ツールは、メモリIPの設計、検証、物理配置、タイミング解析、消費電力解析など、IPの統合プロセス全体を支援します。メモリコンパイラは、ユーザーが指定したサイズ、ポート数、アスペクト比などの要件に基づいて、最適なメモリインスタンスを自動生成するツールであり、設計の柔軟性と効率性を高めます。低消費電力設計技術も重要で、パワーゲーティング、電圧スケーリング、クロックゲーティング、データリテンションモードなど、メモリブロックの消費電力を削減するための様々な手法がIPに組み込まれています。さらに、MBISTなどのテスト容易性設計(DFT)や、製造歩留まりを向上させるためのDFM(Design for Manufacturability)も、高品質なメモリIPには不可欠な要素です。近年では、セキュリティ機能の強化も進んでおり、セキュアブートや物理的複製不能関数(PUF)といった技術がROM IPと連携して、デバイスの信頼性と安全性を高めています。

市場背景としては、IoT、AI、5G通信、データセンター、車載エレクトロニクスといった分野の急速な成長が、SRAMおよびROMデザインIP市場を牽引しています。これらのアプリケーションは、それぞれ異なるメモリ要件を持つため、多様な特性を持つIPの需要が高まっています。特に、SoC内部に組み込まれるエンベデッドメモリの需要は増加の一途をたどっており、外部メモリへのアクセスに伴うレイテンシや消費電力を削減するために、より多くのSRAMやROMがSoCに統合される傾向にあります。IPベンダーは、顧客の特定のニーズに応えるため、カスタマイズ可能でコンフィギュラブルなIPを提供することに注力しています。低消費電力化、高性能化、そしてセキュリティ機能の強化は、市場における主要なトレンドであり、IPベンダー間の競争も激化しています。また、チップレットアーキテクチャの台頭により、異なる機能を持つチップレット間での高速なデータ交換やローカルストレージとして、高性能なメモリIPの重要性がさらに増しています。

将来展望として、SRAMおよびROMデザインIPは、引き続き半導体技術の最前線で進化を続けるでしょう。プロセスノードのさらなる微細化は、メモリセルの物理的な限界に近づいていますが、新しい材料や構造(例えば、ゲートオールアラウンドFET)の導入により、高密度化と低消費電力化は継続されます。また、MRAM(磁気抵抗メモリ)やRRAM(抵抗変化型メモリ)、FeRAM(強誘電体メモリ)といった次世代の不揮発性メモリ技術が、従来のROMやフラッシュメモリの代替、あるいは補完として、エンベデッドメモリ市場に登場する可能性があります。これらの新技術は、高速性、低消費電力、高耐久性を兼ね備え、特にIoTやAIエッジデバイスでの利用が期待されています。さらに、ヘテロジニアスインテグレーションや3Dスタッキング技術の進展により、ロジックとメモリを垂直方向に積層することで、より高い帯域幅と低いレイテンシを実現するメモリIPが登場するでしょう。AI/ML技術は、メモリIPの設計、最適化、検証プロセスにも導入され、より効率的で高性能なIPの開発を加速させると考えられます。セキュリティ機能は、今後もIP設計の重要な要素であり続け、より高度なハードウェアベースのセキュリティ対策がメモリIPに組み込まれていくでしょう。最終的には、特定のアプリケーションに特化したドメインスペシフィックなメモリIPが、AIアクセラレータ、量子コンピューティング、ニューロモルフィックコンピューティングといった新たな分野で重要な役割を果たすことが期待されます。