ハイブリッドメモリキューブ市場 規模・シェア分析 – 成長トレンドと予測 (2025年~2030年)

ハイブリッドメモリキューブ市場レポートは、エンドユーザー産業(エンタープライズストレージ、車載ADASなど)、メモリ容量(2GB~8GB、8GB~16GB、16GB~32GB、32GB超)、アプリケーション(プロセッサキャッシュ、データバッファ、グラフィックスメモリ、産業用およびIoTエッジ)、テクノロジーノード(光インターコネクトHMC、チップレットベースHMCなど)、および地域によって分類されます。市場予測は、金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

ハイブリッドメモリキューブ(HMC)市場の概要を以下にまとめます。

ハイブリッドメモリキューブ市場:規模と予測(2025年~2030年)

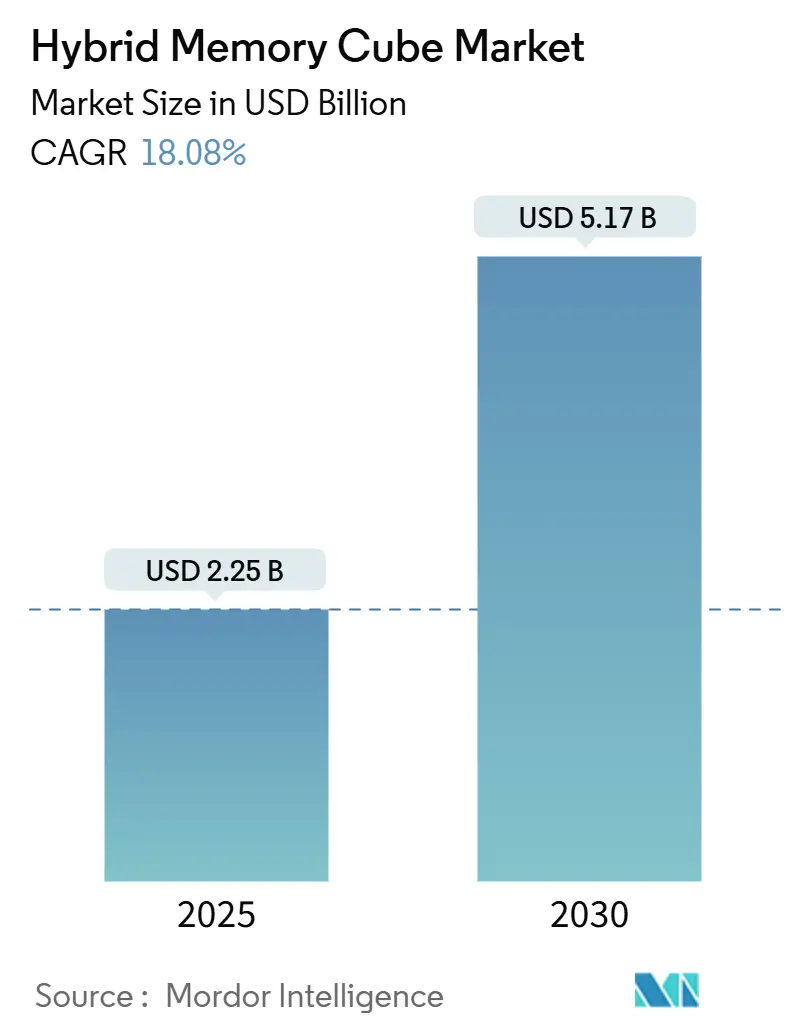

ハイブリッドメモリキューブ(HMC)市場は、2025年に22.5億米ドルと推定され、2030年には51.7億米ドルに達すると予測されており、予測期間(2025年~2030年)中の年平均成長率(CAGR)は18.08%と堅調な拡大が見込まれています。この成長は、AI推論エンジン、高性能コンピューティング(HPC)クラスター、自動運転車向けセンサーフュージョンスタックなどがテラバイト/秒レベルのシステムメモリを要求する中、HMCが従来のDDRやLPDDRの帯域幅の制約を打破する能力を持つことに起因しています。エンタープライズストレージのアップグレード、チップレットベースのヘテロジニアス統合、エクサスケールスーパーコンピューターの展開が市場機会を拡大しており、アジア太平洋地域の製造規模が供給と需要の中心となっています。光インターコネクトのプロトタイプやユニバーサルチップレットインターコネクト規格の登場により、ベンダーロックインが緩和され、潜在的な顧客基盤が拡大するなど、技術競争が激化しています。一方で、TSV(Through-Silicon-Via)プロセスにおける歩留まりの課題や熱管理の複雑さが、短期的なユニットコスト改善を抑制する可能性があります。

主要なレポートのポイント

* エンドユーザー産業別: 2024年にはエンタープライズストレージが市場シェアの41.3%を占め、自動車ADASは2030年までに21.18%のCAGRで拡大すると予測されています。

* メモリ容量別: 2024年には16GB~32GBの層が市場シェアの37.8%を占めました。32GBを超えるモジュールは2030年までに20.23%のCAGRで成長すると予想されています。

* アプリケーション別: 2024年にはプロセッサキャッシュの展開が市場規模の36.8%を占め、産業用およびIoTエッジノードは2025年~2030年の間に20.88%のCAGRで進展すると予測されています。

* テクノロジーノード別: 2024年にはTSVベースの第2世代製品が市場シェアの48.02%を占めましたが、光インターコネクト型は予測期間中に19.87%のCAGRで進展すると予測されています。

* 地域別: 2024年にはアジア太平洋地域が市場シェアの41.22%を占め、2030年までに20.41%のCAGRで成長し、他のすべての地域を上回ると予測されています。

世界のハイブリッドメモリキューブ市場のトレンドと洞察

市場の推進要因

1. AI/HPCワークロードの急速な普及と高帯域幅メモリの需要: 大規模言語モデルのトレーニングは、演算ユニットが飽和する前に計算が停止する「メモリウォール」の問題を浮き彫りにしています。HMCは最大320GB/秒の帯域幅を提供し、GPUやテンソルコアへのデータ供給を維持します。リアルタイム言語翻訳や自動運転向けのエッジ推論は低遅延DRAMの代替を必要とし、垂直積層メモリの需要を確固たるものにしています。IEEEの研究によると、3DインターコネクトはDDR5と比較してビットあたりのエネルギーを40%削減し、大規模クラスターの運用コストを低減します。

2. エンタープライズストレージおよびハイパースケールデータセンターのリフレッシュサイクルの増加: ハイパースケーラーはHDDアレイを計算ストレージプロセッサを統合したオールフラッシュノードに置き換えており、これらのチップは並列NANDチャネルを最小のキュー深度で管理するために帯域幅を必要とします。Intelは、次世代ストレージコントローラが高帯域幅メモリに依存してインライン重複排除、イレージャーコーディング、暗号化を高速化すると強調しています。

3. 5Gコアおよびエッジネットワーキング機器展開の拡大: 5Gコアネットワークにおけるプール型メモリ構造の活用は、ノードあたりの容量ニーズを高めています。

4. 米国、中国、欧州における政府主導のエクサスケールコンピューティングイニシアチブ: 米国エネルギー省のFrontierおよびAuroraシステムは、数千のアクセラレータに一貫した帯域幅を提供する3D積層メモリを利用することで、持続的なエクサフロップス性能を達成しています。これらの公的投資は、商業ベンダーが製品を量産展開する前に改良するための非反復エンジニアリングコストを相殺します。

5. チップレットベースのヘテロジニアス統合アーキテクチャの普及: チップレット設計は複雑なSoCをより小さなダイに分割し、経済的なノード混合と歩留まり改善を可能にします。AMDのEPYCロードマップは、有機インターポーザーを介して接続された積層メモリダイを特徴とし、TSVおよびチップオンウェハーオンサブストレート技術の利点を示しています。UCIe(Universal Chiplet Interconnect Express)規格の最終化は、HMCの採用障壁を低減します。

6. クラウドプラットフォームにおけるコンポーザブルおよびディスアグリゲーテッドサーバーアーキテクチャへの移行: クラウドプラットフォームにおけるコンポーザブルおよびディスアグリゲーテッドサーバーアーキテクチャへの移行は、HMCのような柔軟なメモリソリューションの需要を促進します。

市場の抑制要因

1. 従来のDDRx/LPDDR DRAM技術の強力な優位性: DDR5モジュールの出荷数は2023年に2億ユニットを超え、ギガバイトあたりのコストを3米ドル以下に押し下げ、サプライチェーンの規模の経済を強化しています。サーバーOEMは非DDRインターフェースを導入するために長い認定サイクルを必要とし、多くの企業顧客はリスク回避的な購買方針を維持しています。

2. 高い製造コストとTSV歩留まりの制約: TSVのための深掘り反応性イオンエッチングは、平面DRAMにはない欠陥メカニズムを導入し、SK hynixの2024年決算発表によると、ギガバイトあたりのコストをDDR5と比較して最大60%増加させます。85%未満の歩留まりは冗長性のオーバーヘッドを生み出し、ダイ面積を膨らませ、粗利益を減少させます。

3. 3D積層メモリキューブにおける熱管理の複雑さ: 3D積層メモリキューブは、高密度化により熱管理が複雑になり、性能と信頼性に影響を与える可能性があります。

4. 限られたサプライヤーエコシステムとIPライセンスの摩擦: HMC市場は少数の主要サプライヤーに集中しており、IPライセンスの摩擦が新規参入や技術革新の障壁となる可能性があります。

セグメント分析

* エンドユーザー産業別:エンタープライズストレージがリード、自動車ADASが加速

エンタープライズストレージは2024年の収益の41.3%を占め、ハイパースケールオペレーターがメモリセマンティックストレージコントローラを備えたオールフラッシュアレイを更新していることが背景にあります。自動車ADASワークロードは、レベル3およびレベル4の自律走行に焦点を当て、センサーフュージョンと車載AIが主流になるにつれて、2030年までに21.18%のCAGRで増加すると予測されています。自動車分野の成長は、HMC市場が熱効率と持続的な帯域幅を優先するエッジデバイスへと移行していることを示しています。

* メモリ容量別:ミッドレンジが優勢、高容量が急増

16GB~32GBのモジュールは2024年の展開の37.8%を占め、デュアルソケットサーバーの期待とコストパフォーマンスの最適なバランスに合致しています。32GBを超える容量のHMC市場規模は、大規模言語モデルの推論ノードやNUMAシステムがマルチテラバイトプールを展開するにつれて、20.23%のCAGRで拡大すると予測されています。

* アプリケーション別:プロセッサキャッシュがリード、産業用およびIoTエッジが加速

プロセッサキャッシュの使用は2024年の展開の36.8%を占め、マルチチップサーバープロセッサのニアメモリ高速化を提供しています。産業用およびIoTエッジの採用は20.88%のCAGRで成長すると予測されており、工場自動化やスマートグリッドノードにおける決定論的なリアルタイムワークロードが、厳しい条件下でのマイクロ秒応答を必要としているためです。

* テクノロジーノード別:TSV Gen 2がリード、光インターコネクトが勢いを増す

TSVベースの第2世代設計は、Samsung、SK hynix、Micronにおける供給の成熟度により、2024年に48.02%のシェアを占めました。シリコンフォトニクスがより効率的に統合され、ラック規模のディスアグリゲーテッド設計におけるクロストークを低減するため、光インターコネクト型は19.87%のCAGRで推移しています。

地域分析

* アジア太平洋: 2024年にはHMC市場収益の41.22%を占め、2030年までに20.41%のCAGRで成長すると予測されています。SamsungとSK hynixの集中した製造能力に加え、中国、日本、韓国、インドにおける半導体推進政策が牽引しています。中国政府は国内の積層メモリ革新に150億人民元を投じ、日本の共同投資は2nmノードを通じたチップレットパッケージングを支援しています。

* 北米: 2024年の収益の28%を占め、ハイパースケールクラウドのリフレッシュサイクルとエネルギー省のエクサスケールプログラムが牽引しています。Intelの200億米ドルのオハイオ州拡張は、HMCダイをXeonおよびGPUアセンブリに直接組み込むための高度なパッケージングラインを収容する予定です。

* 欧州: 2024年の収益の約18%を占め、自動車ADASの採用とEuroHPCスーパーコンピューターの設置が牽引しています。ドイツのティアワン企業であるBoschとContinentalは、厳格な遅延予算を満たすために、レベル3の知覚プラットフォームにHMCを組み込んでいます。

競争環境

Samsung、SK hynix、Micronの3つの垂直統合型サプライヤーがHMC容量の70%以上を占めていますが、新規参入企業はチップレット設計と光インターコネクトIPを活用して既存企業に挑戦しています。Samsungは、電気リンクと比較して遅延を30%削減する、シリコンフォトニクスを積層ダイに組み込んだ光インターコネクトプロトタイプでリードしています。Micronは、米国の生産能力を拡大するために61億米ドルのCHIPS法助成金を獲得し、供給の多様性を改善しています。SK hynixは、AIアクセラレータの需要増加への自信を示すため、TSV容量を追加するために40億米ドルを投資しています。

IntelのフォトニックIP買収とFalcon Shores GPUへの統合は、アクセラレータ製品の新たなメモリ供給経路を導入しています。Rambusは、チップレット設計者に高速シリアライザー・デシリアライザーブロックをライセンス供与し、ファブレス企業がアナログ設計のオーバーヘッドなしにHMCインターフェースを組み込むことを可能にしています。UCIeの標準化とJEDEC HBM4の継続的な作業は、積層DRAMファミリーとパケット化されたHMCの境界を曖昧にし、高帯域幅メモリ市場全体のTAM(Total Addressable Market)を拡大する可能性があります。

最近の業界動向

* 2025年10月: Samsung Electronicsが平沢工場で36GB光インターコネクトメモリパッケージの量産を開始。電気SerDesと比較して遅延が30%低いと発表。

* 2025年9月: SK hynixが利川工場でのTSV製造ライン拡張に40億米ドルを投資することを表明。生産は2026年下半期に予定。

* 2025年8月: Intelが、DOEエクサスケールシステムを初期ターゲットとして、フォトニックメモリリンクを統合したFalcon Shores GPUの2026年初頭出荷を発表。

* 2025年7月: Micronが、米国の先進メモリ容量を拡大するために61億米ドルのCHIPS法助成金を獲得。第一段階の完了は2027年までに予定。

このレポートは、ハイブリッドメモリキューブ(HMC)市場に焦点を当て、その市場の動向、成長予測、主要な推進要因と阻害要因、および競争環境について詳細に分析しています。

1. 市場概要と成長予測

ハイブリッドメモリキューブ市場は、2025年から2030年にかけて年平均成長率(CAGR)18.08%で成長し、2030年には51.7億米ドルに達すると予測されています。

2. 市場の推進要因

市場の成長を牽引する主な要因は以下の通りです。

* エンタープライズストレージおよびハイパースケールデータセンターのリフレッシュサイクルが活発化していること。

* AI(人工知能)やHPC(高性能コンピューティング)ワークロードの急速な普及により、高帯域幅メモリの需要が増大していること。

* 5Gコアおよびエッジネットワーキング機器の導入が拡大していること。

* 米国、中国、欧州における政府主導のエクサスケールコンピューティングイニシアチブ。

* チップレットベースのヘテロジニアス統合アーキテクチャが注目を集めていること。

* クラウドプラットフォームにおけるコンポーザブルおよびディスアグリゲーテッドサーバーアーキテクチャへの移行。

3. 市場の阻害要因

一方で、市場の成長を妨げる要因も存在します。

* 従来のDDRx/LPDDR DRAM技術の強い優位性。

* 高い製造コストとTSV(Through-Silicon Via)の歩留まり制約。TSVの歩留まり率は85%を下回っており、DDR5モジュールと比較してギガバイトあたりのコストを最大60%上昇させています。

* 3D積層メモリキューブにおける熱管理の複雑さ。

* 限られたサプライヤーエコシステムとIPライセンスに関する摩擦。

4. 主要セグメントと地域動向

* エンドユーザー産業別: 2024年の収益では、ハイパースケーラーによるオールフラッシュアレイのリフレッシュにより、エンタープライズストレージが41.3%を占め、最大の貢献をしています。その他、通信・ネットワーキング、高性能コンピューティング、車載ADASなどが主要なセグメントです。

* アプリケーション別: 産業用およびIoTエッジノードは、2025年から2030年にかけて20.88%のCAGRで最も速く成長すると予想されています。プロセッサキャッシュ、データバッファ、グラフィックスメモリも重要なアプリケーションです。

* メモリ容量別: 2GB~8GB、8GB~16GB、16GB~32GB、32GB以上といった容量帯で分析されています。

* 技術ノード別: TSVベースのハイブリッドメモリキューブ(Gen 2)、光インターコネクトHMC、チップレットベースHMCが含まれます。UCIeベースのチップレット標準により、HMCをマルチダイパッケージに統合する際の設計が簡素化され、市場投入までの時間が短縮されています。

* 地域別: アジア太平洋地域は、集積された製造能力、政府のインセンティブ、強力なクラウド構築により、20.41%の地域CAGRで最も急速に成長する地域です。北米、南米、欧州、中東・アフリカも分析対象です。

5. 競争環境

市場は、Micron Technology Inc.、Intel Corporation、Samsung Electronics Co., Ltd.、SK hynix Inc.、International Business Machines Corporation、Advanced Micro Devices Inc.など、多数の主要企業によって構成されています。レポートでは、市場集中度、戦略的動向、市場シェア分析、および主要企業のプロファイルが提供されています。

6. 市場機会と将来展望

レポートでは、未開拓の分野や満たされていないニーズの評価を通じて、将来の市場機会についても言及しています。

このレポートは、ハイブリッドメモリキューブ市場の全体像を把握し、将来の戦略立案に役立つ情報を提供しています。

1. はじめに

- 1.1 調査の前提条件と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

-

4.2 市場の推進要因

- 4.2.1 企業ストレージとハイパースケールデータセンターのリフレッシュサイクルの増加

- 4.2.2 高帯域幅メモリを要求するAI / HPCワークロードの急速な普及

- 4.2.3 5Gコアおよびエッジネットワーキング機器の展開の拡大

- 4.2.4 米国、中国、ヨーロッパにおける政府支援のエクサスケールコンピューティングイニシアチブ

- 4.2.5 チップレットベースのヘテロジニアス統合アーキテクチャの普及

- 4.2.6 クラウドプラットフォームにおけるコンポーザブルおよび非集約型サーバーアーキテクチャへの移行

-

4.3 市場の阻害要因

- 4.3.1 従来のDDRx / LPDDR DRAM技術の強力な優位性

- 4.3.2 高い製造コストとTSV歩留まりの制約

- 4.3.3 3D積層メモリキューブにおける熱管理の複雑さ

- 4.3.4 限られたサプライヤーエコシステムとIPライセンスの摩擦

- 4.4 産業バリューチェーン分析

- 4.5 マクロ経済要因の影響

- 4.6 規制環境

- 4.7 技術的展望

-

4.8 ポーターの5つの力分析

- 4.8.1 買い手の交渉力

- 4.8.2 供給者の交渉力

- 4.8.3 新規参入の脅威

- 4.8.4 代替品の脅威

- 4.8.5 競争の激しさ

5. 市場規模と成長予測(金額)

-

5.1 エンドユーザー産業別

- 5.1.1 エンタープライズストレージ

- 5.1.2 電気通信およびネットワーキング

- 5.1.3 ハイパフォーマンスコンピューティング

- 5.1.4 車載ADAS

- 5.1.5 その他のエンドユーザー産業

-

5.2 メモリ容量別

- 5.2.1 2 GB~8 GB

- 5.2.2 8 GB~16 GB

- 5.2.3 16 GB~32 GB

- 5.2.4 32 GB以上

-

5.3 アプリケーション別

- 5.3.1 プロセッサキャッシュ

- 5.3.2 データバッファ

- 5.3.3 グラフィックスメモリ

- 5.3.4 産業用 / IoTエッジ

-

5.4 テクノロジーノード別

- 5.4.1 TSVベースのハイブリッドメモリキューブ (第2世代)

- 5.4.2 光インターコネクトHMC

- 5.4.3 チップレットベースHMC

-

5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米諸国

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 スペイン

- 5.5.3.6 ロシア

- 5.5.3.7 その他のヨーロッパ諸国

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 インド

- 5.5.4.4 韓国

- 5.5.4.5 オーストラリア

- 5.5.4.6 その他のアジア太平洋諸国

- 5.5.5 中東およびアフリカ

- 5.5.5.1 中東

- 5.5.5.1.1 サウジアラビア

- 5.5.5.1.2 アラブ首長国連邦

- 5.5.5.1.3 トルコ

- 5.5.5.1.4 その他の中東諸国

- 5.5.5.2 アフリカ

- 5.5.5.2.1 南アフリカ

- 5.5.5.2.2 ナイジェリア

- 5.5.5.2.3 エジプト

- 5.5.5.2.4 その他のアフリカ諸国

6. 競争環境

- 6.1 市場集中度

- 6.2 戦略的動き

- 6.3 市場シェア分析

-

6.4 企業プロファイル(グローバルレベルの概要、市場レベルの概要、コアセグメント、利用可能な財務情報、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 マイクロン・テクノロジー株式会社

- 6.4.2 インテル株式会社

- 6.4.3 サムスン電子株式会社

- 6.4.4 SKハイニックス株式会社

- 6.4.5 インターナショナル・ビジネス・マシーンズ株式会社

- 6.4.6 アドバンスト・マイクロ・デバイセズ株式会社

- 6.4.7 ザイリンクス株式会社

- 6.4.8 富士通株式会社

- 6.4.9 マーベル・テクノロジー株式会社

- 6.4.10 ランバス株式会社

- 6.4.11 ブロードコム株式会社

- 6.4.12 ケイデンス・デザイン・システムズ株式会社

- 6.4.13 ASEテクノロジー・ホールディング株式会社

- 6.4.14 セムテック株式会社

- 6.4.15 オープン・シリコン株式会社

- 6.4.16 アーム株式会社

- 6.4.17 アルテラ株式会社(インテルPSG)

- 6.4.18 台湾積体電路製造株式会社

- 6.4.19 株式会社日立製作所

- 6.4.20 ルネサスエレクトロニクス株式会社

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

ハイブリッドメモリキューブ(Hybrid Memory Cube、略称HMC)は、従来のDRAMの性能限界を打破し、高帯域幅と低消費電力を実現するために開発された革新的なメモリ技術です。複数のDRAMダイを垂直に積層し、その下に高速なインターフェースロジックを搭載したベースダイを配置するという、3次元積層技術(3Dスタッキング)を特徴としています。この積層されたダイ間は、シリコン貫通ビア(TSV: Through-Silicon Via)と呼ばれる微細な垂直配線によって電気的に接続されており、これにより、従来のDDR SDRAMが抱えていたメモリとプロセッサ間のデータ転送速度のボトルネックを解消し、劇的な帯域幅の向上と電力効率の改善を目指しました。HMCは、Micron TechnologyとSamsung Electronicsが中心となって設立されたHMCコンソーシアムによって標準化が進められ、次世代の高性能コンピューティングシステム向けメモリとして大きな期待が寄せられました。

HMCには、厳密な意味での「種類」というよりは、技術の進化と仕様のバージョンアップが存在しました。初期のHMC 1.0仕様から、より高速なデータ転送速度と改善された電力効率を提供するHMC 2.0へと進化しました。HMCのインターフェースは、従来のDDR SDRAMが採用していたパラレルバスとは異なり、高速なシリアルリンクを使用します。これにより、ピン数を大幅に削減しつつ、高いデータ転送レートを実現しました。また、HMCモジュールは、複数のDRAMスタックとベースダイを統合した単一のパッケージとして提供され、システム設計の簡素化にも貢献すると考えられました。HMCは、メモリコントローラをベースダイに内蔵することで、プロセッサ側のメモリコントローラ設計の複雑さを軽減し、より効率的なメモリ管理を可能にするという特徴も持っていました。

HMCの主な用途としては、高いメモリ帯域幅と低消費電力が不可欠な高性能コンピューティング(HPC)分野、データセンター、ネットワーク機器、グラフィックス処理ユニット(GPU)、そして人工知能(AI)アクセラレータなどが挙げられました。特に、ビッグデータ解析、機械学習、科学技術計算、リアルタイムシミュレーションなど、大量のデータを高速に処理する必要があるアプリケーションにおいて、HMCはメモリウォール問題(プロセッサの性能向上にメモリの帯域幅が追いつかない問題)を解決する有力なソリューションとして期待されました。プロセッサとメモリ間のデータ転送効率を向上させることで、システム全体のパフォーマンスを最大化し、より複雑で大規模な計算を可能にすることがHMCの目標でした。

HMCに関連する技術としては、まずその基盤となる「3次元積層技術(3Dスタッキング)」と「シリコン貫通ビア(TSV)」が挙げられます。これらは、複数の半導体ダイを垂直に積み重ね、高密度かつ高速に接続するための不可欠な技術です。HMCと並行して開発され、後にHMCよりも広く普及した「HBM(High Bandwidth Memory)」も、同様に3DスタッキングとTSVを利用して高帯域幅を実現するメモリ技術です。HBMは、HMCとは異なるインターフェースとアーキテクチャを採用しており、特にGPUやAIアクセラレータの分野でデファクトスタンダードとしての地位を確立しました。また、従来のグラフィックス用途で広く使われる「GDDRシリーズ」も広帯域幅メモリの一種ですが、HMCやHBMとは異なり、パラレルインターフェースを主としています。これらの技術はすべて、メモリウォール問題を克服し、プロセッサの性能を最大限に引き出すための広帯域幅メモリという共通の目標を持っています。

HMCの市場背景は、2000年代後半から2010年代初頭にかけて顕在化した「メモリウォール」問題に深く根ざしています。プロセッサの処理能力がムーアの法則に従って指数関数的に向上する一方で、従来のDDR SDRAM技術では、その性能を十分に引き出すためのメモリ帯域幅の向上が追いつかなくなっていました。このボトルネックが、システム全体の性能向上を阻害する主要因となっていたのです。この課題を解決するため、Micron TechnologyとSamsung Electronicsが中心となり、2011年にHMCコンソーシアムが設立され、HMCの標準化と普及が推進されました。HMCは、従来のDDR SDRAMと比較して、大幅な帯域幅の向上と電力効率の改善を謳い、次世代の高性能システム向けメモリとして大きな期待を集めました。しかし、同時期に開発が進められていたHBMが、AMDやNVIDIAといった主要なGPUベンダーとの連携を深め、より早期に市場投入されたことで、特にグラフィックスやAIアクセラレータの分野でHBMが優位に立ちました。HMCは、その技術的な優位性にもかかわらず、HBMとの競合、製造コストの高さ、そしてエコシステムの構築の難しさなどから、大規模な普及には至りませんでした。

HMCの将来展望について言えば、特定の製品としてのHMCは、その革新的な技術コンセプトにもかかわらず、市場での普及という点ではHBMに一歩譲る形となりました。Micron Technologyは2018年にHMCの生産終了を発表し、事実上、HMCの市場展開は終息しました。しかし、HMCが提唱した3次元積層技術、TSV、そしてメモリとロジックの統合による高帯域幅・低消費電力化というコンセプトは、その後のHBMやその他の広帯域幅メモリ技術に計り知れない影響を与えました。HMCの技術的な遺産は、HBM3や将来のメモリ技術、例えばCXL(Compute Express Link)のような新しいインターフェースと組み合わせたメモリ拡張技術などに引き継がれています。メモリとプロセッサ間のボトルネックを解消し、システム全体の性能を向上させるというHMCの目標は、今後も様々な形で追求されていくでしょう。HMCは、特定の製品としては終息しましたが、その技術思想と挑戦は、現代の高性能コンピューティングを支えるメモリ技術の発展に不可欠な一歩であり、その功績は高く評価されるべきです。