パネルレベルパッケージング市場 規模・シェア分析 – 成長動向と予測 (2025-2030年)

パネルレベルパッケージング市場レポートは、パッケージング技術(ファンアウトパネルレベルパッケージング、エンベデッドブリッジなど)、基板材料(有機ラミネート、ガラスコアなど)、パネルサイズ(300mm×300mm以下、301-510mm×510mm、511mm×600mm以上)、産業用途(家電、自動車など)、および地域(北米、ヨーロッパなど)によってセグメント化されています。市場予測は、金額(米ドル)で提供されます。

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

本レポートは、パネルレベルパッケージング市場の規模、シェア、業界分析を詳細に概説しています。市場はパッケージング技術、基板材料、パネルサイズ、産業用途、地域別にセグメント化され、2025年から2030年までの市場予測が米ドル価値で提供されています。

市場概要

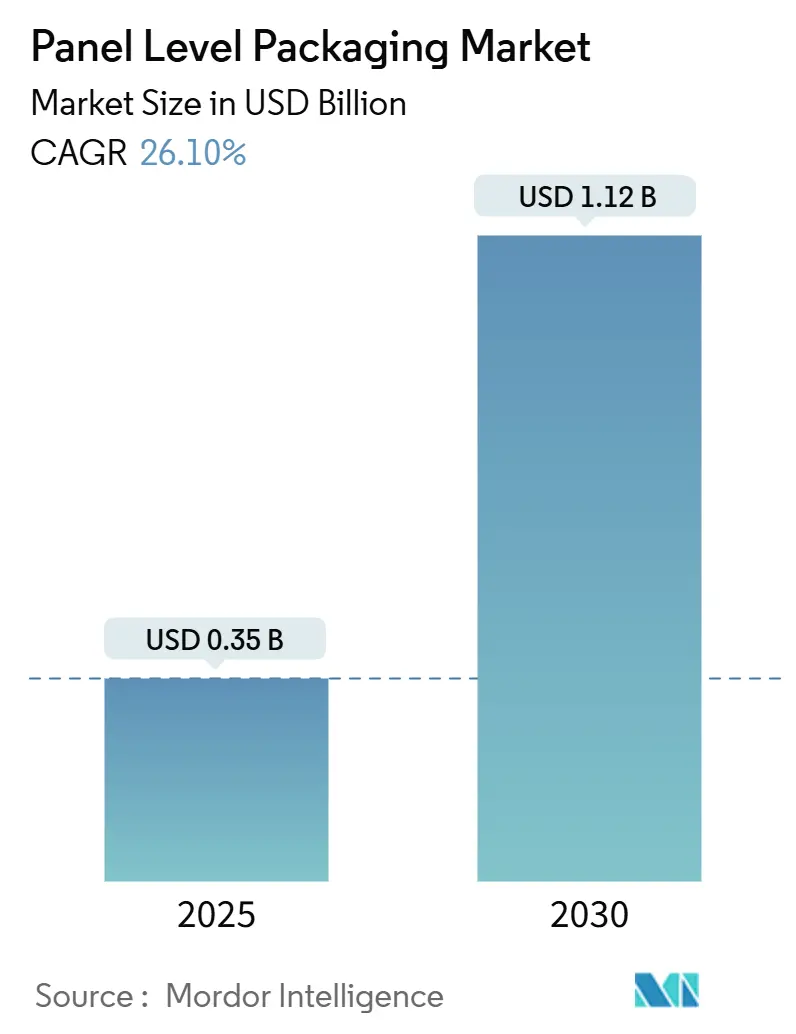

パネルレベルパッケージング市場は、2025年の0.35億米ドルから2030年には1.12億米ドルへと成長し、予測期間中のCAGRは26.10%に達すると見込まれています。アジア太平洋地域が最も急速に成長し、最大の市場であり、市場集中度は中程度です。主要企業には、ASE Technology Holding Co., Ltd.、Taiwan Semiconductor Manufacturing Company Limited (TSMC)、Samsung Electronics Co., Ltd.、Amkor Technology, Inc.、Intel Corporationなどが含まれます。この急成長は、半導体業界がウェハー中心からパネル中心のアーキテクチャへと移行し、AIや高性能コンピューティング(HPC)の需要増大に対応して規模の優位性を追求していることを反映しています。パネルフォーマットはマルチダイ設計において最大40%の基板利用率向上を実現し、コスト圧力を緩和します。ガラスコア基板への移行などの基板革新は、より厳密な寸法制御と熱安定性をもたらし、I/O数の増加をサポートしています。

市場の成長要因

市場の成長を牽引する主な要因は以下の通りです。

本レポートは、先進パッケージング技術であるパネルレベルパッケージング(PLP)市場に関する詳細な分析を提供しています。PLPは、ファンアウトウェハーレベルパッケージング(FOWLP)の次なるステップとして位置づけられており、ウェハー形状ではなく長方形のパネル形式を採用することで、プロセスステップの並列化とパッケージの面積利用率向上を実現し、材料廃棄物を削減することで大幅なコスト優位性をもたらすと期待されています。世界中のベンダーは、450mm FOWLPのロードマップを策定する代わりに、PLPのスケールアップに注力しています。

PLP市場は、2025年の3.5億米ドルから2030年には11.2億米ドルへと成長し、予測期間中に年平均成長率(CAGR)26.1%を記録すると予測されています。地域別では、アジア太平洋地域が2024年の収益の69.9%を占め、2030年まで最も急速に拡大する地域であり続ける見込みです。

市場の成長を牽引する主な要因としては、ウェハーレベルパッケージングと比較したコスト削減効果、AI/HPC(高性能コンピューティング)チップ需要の急増、5G/6Gおよびエッジデバイスの普及が挙げられます。また、Nikonの600mm x 600mmデジタルリソグラフィ技術の採用、2026年以降のガラスコア基板への移行、そして先進パッケージングに関連するEU/米国での国内回帰(リショアリング)補助金も重要な推進力となっています。特にガラスコアは、優れた寸法安定性と低い誘電損失により、AIおよび6Gデバイス向けにより高密度な配線を実現するため注目されています。

一方で、市場にはいくつかの課題も存在します。高い設備投資と反り(warpage)の問題、300mmを超えるパネルでのプロセス統合の複雑さ、大型パネルにおけるサブ1µmリソグラフィの歩留まり低下、ABF-GCP誘電体フィルムの供給ボトルネックなどが挙げられます。特に、300mmを超える大型パネルでは、反りの制御とサブミクロンリソグラフィの歩留まりの崖が主要な製造上の課題となっています。

本レポートでは、PLP市場を以下の主要なセグメントに分けて分析しています。パッケージング技術別(ファンアウトパネルレベルパッケージング、エンベデッドブリッジ、2.5D/3Dパネル統合、ファンインパネルレベルパッケージング)、基板材料別(有機ラミネート、ガラスコア、シリコン、モールド再構成パネル)、パネルサイズ別(≤300mm x 300mm、301mm – 510mm x 510mm、≥511mm x 600mm)、産業アプリケーション別(消費者向け電子機器、自動車、通信、航空宇宙・防衛、産業・IoT)、地域別(北米、南米、欧州、アジア太平洋、中東、アフリカ)です。この中で、自動車のADAS(先進運転支援システム)およびEVパワーモジュール分野は、2030年までに年平均成長率28.8%で最も高い成長を示すと予測されています。

競争環境については、Samsung Electronics、TSMC、Intel、ASE Technology Holding、Amkor Technology、Nikon Corporation、Ajinomoto Fine-Technoなど、多数の主要企業がプロファイルされています。また、米国のCHIPS法による資金提供は、国内のパネル生産能力を加速させ、北米の防衛およびクラウド顧客向けのサプライチェーンの回復力を強化すると見られています。

パネルレベルパッケージング市場は、コスト効率と技術革新により、今後も力強い成長が期待される分野です。特にAI/HPCや5G/6Gといった次世代技術の進展が需要を押し上げ、ガラスコア基板のような新材料の採用が進む一方で、製造上の複雑性や供給課題への対応が成功の鍵となるでしょう。

1. はじめに

- 1.1 調査の前提と市場の定義

- 1.2 調査範囲

2. 調査方法

3. エグゼクティブサマリー

4. 市場概況

- 4.1 市場概要

-

4.2 市場の推進要因

- 4.2.1 ウェハーレベルパッケージングに対するコスト削減

- 4.2.2 AI/HPCチップ需要の急増

- 4.2.3 5G/6Gおよびエッジデバイスの普及

- 4.2.4 ニコン製600 x 600 mmデジタルリソグラフィの採用

- 4.2.5 2026年以降のガラスコア基板への移行

- 4.2.6 高度なパッケージングに関連するEU/米国リショアリング補助金

-

4.3 市場の阻害要因

- 4.3.1 高い設備投資と反り問題

- 4.3.2 300 mmを超えるプロセス統合の複雑さ

- 4.3.3 大型パネルにおける1 µm未満のリソグラフィ歩留まりの急落

- 4.3.4 ABF-GCP誘電体フィルムの供給ボトルネック

- 4.4 産業バリューチェーン分析

- 4.5 規制環境

- 4.6 技術的展望

-

4.7 ポーターの5つの力分析

- 4.7.1 供給者の交渉力

- 4.7.2 買い手の交渉力

- 4.7.3 新規参入の脅威

- 4.7.4 代替品の脅威

- 4.7.5 競争の激しさ

5. 市場規模と成長予測(金額)

-

5.1 パッケージング技術別

- 5.1.1 ファンアウトパネルレベルパッケージング (FOPLP)

- 5.1.2 エンベデッドブリッジ (eBridge)

- 5.1.3 2.5D/3Dパネル統合

- 5.1.4 ファンインパネルレベルパッケージング

-

5.2 基板材料別

- 5.2.1 有機積層板

- 5.2.2 ガラスコア

- 5.2.3 シリコン

- 5.2.4 成形再構成パネル

-

5.3 パネルサイズ別

- 5.3.1 ≤300 mm × 300 mm

- 5.3.2 301 – 510 mm × 510 mm

- 5.3.3 ≥511 mm × 600 mm

-

5.4 産業用途別

- 5.4.1 家庭用電化製品

- 5.4.2 自動車 (ADAS、EVパワー)

- 5.4.3 電気通信 (5G/6Gインフラ)

- 5.4.4 航空宇宙および防衛

- 5.4.5 産業およびIoT

-

5.5 地域別

- 5.5.1 北米

- 5.5.1.1 米国

- 5.5.1.2 カナダ

- 5.5.1.3 メキシコ

- 5.5.2 南米

- 5.5.2.1 ブラジル

- 5.5.2.2 アルゼンチン

- 5.5.2.3 その他の南米地域

- 5.5.3 ヨーロッパ

- 5.5.3.1 ドイツ

- 5.5.3.2 イギリス

- 5.5.3.3 フランス

- 5.5.3.4 イタリア

- 5.5.3.5 その他のヨーロッパ地域

- 5.5.4 アジア太平洋

- 5.5.4.1 中国

- 5.5.4.2 日本

- 5.5.4.3 韓国

- 5.5.4.4 インド

- 5.5.4.5 その他のアジア太平洋地域

- 5.5.5 中東

- 5.5.5.1 サウジアラビア

- 5.5.5.2 アラブ首長国連邦

- 5.5.5.3 その他の中東地域

- 5.5.6 アフリカ

- 5.5.6.1 南アフリカ

- 5.5.6.2 その他のアフリカ地域

6. 競合情勢

- 6.1 市場集中度

- 6.2 戦略的動向

- 6.3 市場シェア分析

-

6.4 企業プロファイル(グローバル概要、市場概要、主要セグメント、財務情報(入手可能な場合)、戦略情報、主要企業の市場ランキング/シェア、製品とサービス、および最近の動向を含む)

- 6.4.1 Samsung Electronics Co., Ltd.

- 6.4.2 Taiwan Semiconductor Manufacturing Company Limited (TSMC)

- 6.4.3 Intel Corporation

- 6.4.4 ASE Technology Holding Co., Ltd.

- 6.4.5 Amkor Technology, Inc.

- 6.4.6 Powertech Technology Inc.

- 6.4.7 Nepes Corporation

- 6.4.8 Unimicron Technology Corp.

- 6.4.9 DECA Technologies, Inc.

- 6.4.10 JCET Group Co., Ltd.

- 6.4.11 Fraunhofer Institute for Reliability and Microintegration IZM

- 6.4.12 Nikon Corporation

- 6.4.13 Ajinomoto Fine-Techno Co., Inc.

- 6.4.14 Shinko Electric Industries Co., Ltd.

- 6.4.15 LG Innotek Co., Ltd.

- 6.4.16 K&S (Kulicke & Soffa Industries, Inc.)

- 6.4.17 Veeco Instruments Inc.

- 6.4.18 Applied Materials, Inc.

- 6.4.19 Ultratech (Veeco)

- 6.4.20 Tokyo Electron Limited

- 6.4.21 Brewer Science, Inc.

7. 市場機会と将来展望

*** 本調査レポートに関するお問い合わせ ***

パネルレベルパッケージングとは、半導体チップを個別にパッケージングするのではなく、大型の矩形基板(パネル)上で多数のチップを同時にパッケージングする技術の総称でございます。従来のウェハーレベルパッケージング(WLP)が円形のシリコンウェハーを基板とするのに対し、パネルレベルパッケージング(PLP)はより大きな矩形パネルを使用することで、生産効率とコスト効率を大幅に向上させることを目指しています。この技術は、特にファンアウト型パッケージングにおいてその真価を発揮し、半導体パッケージの小型化、薄型化、高性能化、そして低コスト化を実現する次世代の基盤技術として注目されています。

パネルレベルパッケージングにはいくつかの種類がございます。最も注目されているのが、ファンアウト型パネルレベルパッケージング(FOPLP)です。これは、チップの外部に再配線層(RDL: Re-Distribution Layer)を形成することで、より多くの入出力端子(I/O)を引き出し、高密度な接続を可能にする技術です。FOPLPには、まずチップをパネル上に配置してからモールド樹脂で封止し、その上にRDLを形成する「チップファースト」方式と、RDLを形成した基板にチップを埋め込む「RDLファースト」方式などがございます。チップファースト方式は比較的シンプルなプロセスで実現可能ですが、チップの配置精度が重要となります。一方、RDLファースト方式は、より微細なRDL形成が可能であり、高密度なパッケージングに適しています。FOPLPは、チップサイズよりも大きなパッケージフットプリントを持つため、より多くのI/Oを確保できる利点があります。これに対し、ファンイン型パネルレベルパッケージング(FIPLP)は、RDLがチップサイズ内に収まるタイプで、主にMEMSセンサーやRFデバイスなど、I/O数が比較的少ないデバイスの小型化に貢献します。また、受動部品をパネル基板内に埋め込む埋め込み型受動部品(Embedded Passives)技術や、複数の異なるチップを一つのパッケージに統合するシステムインパッケージ(SiP)をパネルレベルで実現する技術も、広義のパネルレベル実装技術として発展しています。

この技術の用途は多岐にわたります。最も大きな市場の一つは、スマートフォンやタブレット、ウェアラブルデバイスなどのモバイル機器です。これらのデバイスでは、プロセッサ、メモリ、RFモジュールなどにPLPが採用され、デバイスの薄型化、小型化、高性能化、そしてバッテリー持続時間の延長に貢献しています。次に、自動車分野では、ADAS(先進運転支援システム)や自動運転、インフォテインメントシステム、EV(電気自動車)のパワーモジュールなどにPLPが適用され始めています。自動車用途では、高い信頼性、耐熱性、そしてコスト効率が求められるため、PLPの堅牢性と生産性が大きなメリットとなります。さらに、データセンターやAIアクセラレータ、HPC(高性能計算)分野では、高帯域幅、低遅延、高電力効率が要求されるため、PLPによる高密度な異種統合パッケージングが不可欠となっています。IoTデバイスや医療機器においても、低コスト、小型、低消費電力といったPLPの特性が活かされています。

パネルレベルパッケージングの実現には、様々な関連技術が不可欠です。まず、再配線層(RDL)技術は、微細な配線パターンを多層に形成し、チップと外部端子を高密度に接続するために極めて重要です。次に、大型パネル上で多数のチップを正確に配置するための高精度アライメント技術が求められます。数ミクロンオーダーの精度が要求されることも珍しくありません。また、チップを封止するモールド技術も重要で、大型パネルでの反りや応力を抑制し、高い平坦性を確保する必要があります。微細なビア(貫通孔)形成やパネルの切断には、レーザー加工技術が活用されます。さらに、製造プロセスにおける欠陥検出や寸法測定には、高度な検査・測定技術が不可欠です。材料技術も重要な要素であり、低誘電率の絶縁材料、低熱膨張係数の封止材、高信頼性の接着剤などがPLPの性能と信頼性を左右します。そして、異なる機能を持つチップ(ロジック、メモリ、RFなど)を効率的に統合する異種統合技術は、PLPの価値を最大限に引き出す上で中心的な役割を担っています。

パネルレベルパッケージングが注目される市場背景には、いくつかの要因がございます。第一に、半導体チップの微細化(ムーアの法則)が物理的・経済的な限界に近づいていることです。これに伴い、チップ単体の性能向上だけでなく、パッケージング技術による性能向上や機能統合が重要視されるようになりました。第二に、異なる機能を持つチップを効率的に統合するヘテロジニアスインテグレーションの進展です。PLPは、多様なチップを一つのパッケージに集積する上で、優れたプラットフォームを提供します。第三に、スマートフォンなどのコンシューマー製品における激しい価格競争と、それに伴うコスト削減圧力です。ウェハーレベルからパネルレベルへの移行は、一度に処理できるチップ数を大幅に増やすことで、生産スループットを向上させ、製造コストを削減する大きな可能性を秘めています。第四に、デバイスの小型化・薄型化要求と、AIや5G/6G通信、HPCといった高性能化要求が同時に高まっていることです。PLPは、高密度な配線と多ピン化を可能にすることで、これらの要求に応えることができます。

将来展望として、パネルレベルパッケージングは今後も技術革新と市場拡大が期待されています。しかし、いくつかの技術的課題も存在します。最も大きな課題の一つは、大型パネルでの反り制御です。異なる材料の熱膨張係数の違いにより発生する反りをいかに抑制し、高精度なプロセスを維持するかが重要です。また、大型パネル全体で均一な高精度チップ配置とRDL形成を実現するための装置技術やプロセス技術のさらなる進化が求められます。材料の選択と長期的な信頼性確保も重要な課題であり、特に自動車用途などでは厳しい環境下での動作保証が必要です。さらに、業界全体での標準化の推進も、PLPの普及を加速させる上で不可欠となります。

今後の進化としては、RDLのさらなる微細化と多層化が進み、より高密度なパッケージングが可能になるでしょう。また、TSV(Through-Silicon Via)などの3Dパッケージング技術との融合により、さらなる高集積化と性能向上が期待されます。新しい材料の導入や、より環境負荷の低い製造プロセスの開発も進むでしょう。応用分野は、AI、HPC、自動運転、5G/6G通信、メタバースといった次世代アプリケーションにおいて、PLPが中心的な役割を果たすことが予想されます。サプライチェーン全体での協力体制が強化され、PLP技術の成熟と普及が加速することで、半導体産業のさらなる発展に大きく貢献していくものと考えられます。